Триггер в процессоре это

Триггер — простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов. Триггер может быть описан конечным автоматом, который способен хранить 1 бит данных, а также выполнять с ним различные операции в зависимости от входных сигналов. Последовательностными называют [1] такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти. Триггер — один из базовых (основных) элементов цифровой техники.

Типы триггеров и принцип их работы

Существует несколько основных типов триггеров. Перед тем, как разобраться в различиях, следует отметить общее свойство: при подаче питания выход любого устройства устанавливается в произвольное состояние. Если это критично для общей работы схемы, надо предусматривать цепи предустановки. В простейшем случае это RC-цепочка, которая формирует сигнал установки начального состояния.

Классификация

Триггерные схемы классифицируют по следующим признакам:

- способу приёма логических сигналов;

- функциональным возможностям;

- принципу построения;

- числу устойчивых состояний (обычно устойчивых состояний два, реже - больше, см. троичный триггер, четверичный триггер [2] , декатрон);

- числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах [3] .

По способу работы с сигналами различают асинхронные, синхронные и смешанные триггерные схемы, статические и динамические.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт». Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двух-ступенчатые (двухтактные).

В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ.

По структурному построению — однотактные (триггеры защёлки), двухтактные и триггеры с динамическим управлением. По способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые. По функциональному назначению — RS, D, JK, T, RR, SS, EE, DV.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно полевые транзисторы), в прошлом — электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС).

Используются в основном в вычислительной технике для организации компонентов вычислительных систем: процессоров, регистров, счётчиков, ОЗУ.

По функциональным возможностям триггеры разделяют на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS-триггеры). Если триггер является синхронным — добавляется вход синхронизации C.;

- универсальные (JK-триггеры);

- с приёмом информации по одному входу D (D-триггеры, или триггеры задержки);

- со счётным входом Т (Т-триггеры).

Каждый тип триггера имеет собственную таблицу работы (таблицу истинности). Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1).

Если триггер синхронный, то существует также дополнительный вход синхронизации. Для того, чтобы такой триггер учёл информацию на синхронных входах, на входе синхронизации необходимо сформировать активный фронт (обычно положительный фронт).

- S (от англ.Set , установить) — вход в RS-триггере;

- R (от англ.Reset , сброс) — вход в RS-триггере;

- J (от англ.Jump[4] , прыжок) — вход в JK-триггере;

- К (от англ.Kill , убить) — вход в JK-триггере;

- Т (от англ.Toggles , переключить) — счётный вход в Т-триггере;

- С (от англ.Clock , время) вход синхронизирующего сигнала. При тактировании по фронту он часто обозначается стрелкой: стрелка внутрь — тактирование по переднему фронту, наружу — по заднему.

- D (от англ.Delay , задержка) — вход в D-триггере;

- E или EN (от англ.Enable , разрешить) — дополнительный асинхронный управляющий вход для разрешения приёма информации (иногда используют букву V).

Содержание

![Схема работы синхронного T-триггера.]()

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

Практическое использование

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Что такое компаратор напряжения и для чего он нужен

Режимы работы, описание характеристик и назначение выводов микросхемы NE555

Что такое операционный усилитель?

Что такое термистор, их разновидности, принцип работы и способы проверки на работоспособность

Любые данные в компьютере — это нули и единички. Текст, который вы читаете прямо сейчас, передался с нашего сервера прямо на ваш компьютер и записался в памяти — он представляет собой последовательность нулей и единичек. Прямо сейчас вы смотрите на ваш монитор, который состоит из пикселей и отображает наш сайт. Изображение — это тоже нули и единицы. Видео — это нули и единицы. Музыка — нули и единицы. Любой контент, доступный на вашем компьютере можно представить в виде нулей и единиц. Но как?

Оперативная память — это сложное устройство, и знать его работу будет полезно каждому

Стоит начать с того, что компьютер понимает только двоичную систему счисления. В жизни мы используем десятичную, так как у нас 10 пальцев и нам она попросту удобнее, но у компьютера нет 10 пальцев — он может работать только с логическими устройствами, которые работают только в двух состояниях — включен или выключен, есть подача тока или нет подачи тока. Если логическое устройство активно, значит подача тока есть и бит равен единице, если подачи тока нет, значит бит равен нулю. Бит — это самая маленькая единица измерения. 1 бит может иметь всего два состояния 1 и 0. 1 байт — это 8 бит. Таким образом, если перебрать все возможные комбинации нулей и единиц, получим, что в 1 байте может храниться 256 комбинаций битов или 2 в степени 8. Например, «0000001», «0000010» или «10110010» — любую букву английского алфавита можно представить в виде 8 битов (1 байта).

Двоичный код выглядит именно так!

Благодаря различным кодировкам мы можем представить любую информацию в двоичном виде. То же касается и наших программ, написанных на различных языках программирования. Чтобы запустить какую-либо программу, её необходимо скомпилировать в двоичный код. Таким образом, в двоичном виде можно представлять как данные, так и инструкции (код) для работы с этими данными. Существуют еще и интерпретируемые языки (JavaScript, Python), в этом случае интерпретатор по ходу выполнения программы анализирует код и компилирует его в язык, понятный нашему компьютеру, то есть в последовательность нулей и единиц, и в этом случае нет необходимости компилировать программу каждый раз при желании запустить её.

Триггерные схемы с несколькими устойчивыми состояниями

Триггер с числом устойчивых состояний N строится из N элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путём соединения выхода каждого элемента (Q0, Q1, . Q(N-1)) с соответствующими входами всех других элементов.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном коде (на выходе Q одного из элементов - "1", на выходах Q других элементов - "0").

Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде (на выходе Q одного из элементов - "0", на выходах Q других элементов - "1").

При добавлении N транзисторов доступа эти триггеры могут работать как ячейки статической сверхоперативной памяти ([6] .

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

История

Рис.1 Схемы из патента Икклза и Джордана 1918 г., один (фиг.1) нарисован как два инвертирующих каскада усилителя с положительной обратной связью, другой (фиг.2) как симметричная перекрёстносвязанная пара.

- 1918 г. М.А.Бонч-Бруевич предложил схему переключающего устройства, имеющего два устойчивых рабочих состояния. Это устройство впоследствии было названо триггером.

- 1918 г. У.Икклз и Ф.Джордан (США) независимо от Бонч-Бруевича изобрели электронное реле (flip-flop, флип-флоп, триггер).

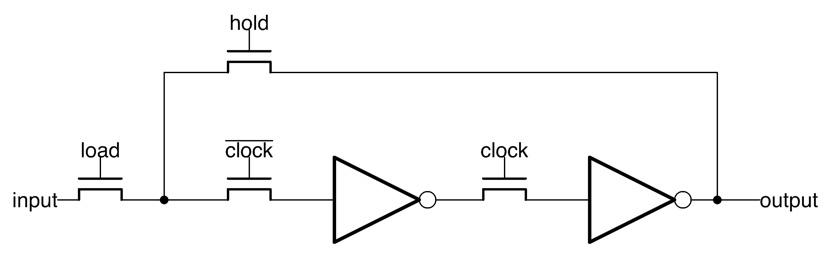

Как работает динамическая защёлка

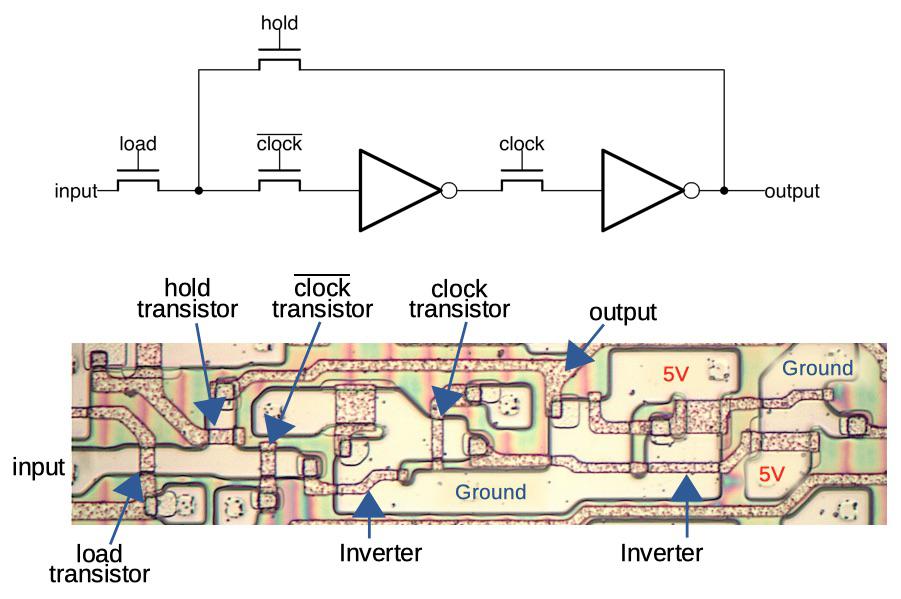

Защёлка – один их важнейших элементов 8086, поскольку защёлки отслеживают то, чем занят процессор. Защёлки можно делать разными способами; в 8086 используется компактная цепь, известная, как динамическая защёлка. Динамическая защёлка зависит от работы двухфазного генератора тактовых импульсов, который часто использовался для управления микропроцессорами той эпохи. Двухфазный генератор тактовых импульсов выдаёт два тактовых сигнала, активных по очереди. В первой фазе основной тактовый сигнал высокий, а сопутствующий тактовый сигнал – низкий. Потом они меняются местами. Цикл повторяется на тактовой частоте, к примеру, 5 МГц.

Многие микропроцессоры используют логические элементы И-НЕ (NAND gates) для формирования RS-триггеров. RS-триггер обычно занимает больше места, чем динамическая защёлка, особенно если к нему добавляются дополнительные цепи для поддержки тактовой частоты. Также популярны D-триггеры (триггеры задержки), однако они получаются ещё более сложными и используют шесть затворов. Во многих случаях достаточно проходного транзистора; он может хранить значение в течение одного такта, но длительного хранения не обеспечивает.

Для процессоров всегда выбирают максимально возможную тактовую частоту. Первый 8086 работал на частоте до 5 МГц, а позже 8086-1 поддерживал уже до 10 МГц. Однако из-за использования динамической логики у 8086 есть ещё и минимальная тактовая частота: 2 МГц. Если генератор тактовых импульсов будет работать медленнее, появится риск утечки заряда с проводников до того, как схемы обратятся к нему, что приведёт к ошибкам.

Защёлка в процессоре 8086 состоит из четырёх проходных транзисторов и двух инверторов. Защёлка работает на перемежающихся тактовых сигналах.

На схеме выше показана типичная защёлка в 8086. Она состоит из двух инверторов и несколько проходных транзисторов. Для наших целей проходной транзистор можно считать выключателем: если на затвор приходит 1, транзистор передаёт сигнал далее. Если приходит 0, транзистор блокирует сигнал. Проходной транзистор управляются несколькими сигналами: загрузка (load), загружающий бит в защёлку; удержание (hold), удерживающий имеющееся значение бита; тактовый сигнал (clock) первой фазы и тактовый сигнал второй, инвертированной.

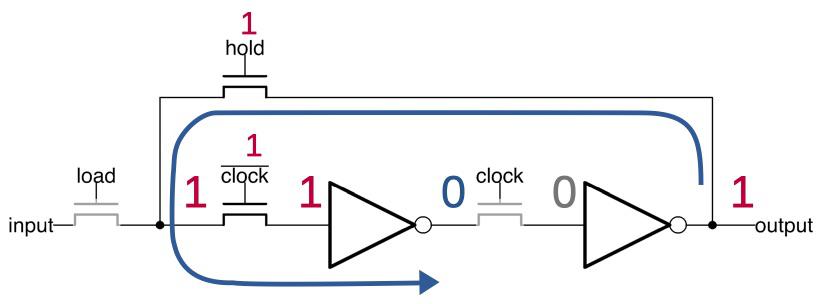

На диаграмме ниже показано, как в защёлку загружается значение (в данном случае, это 1). Для сигнала загрузки повышается напряжение, что позволяет входному сигналу (1) пройти через транзистор. Поскольку тактовый сигнал высокий, сигнал проходит через второй транзистор к инвертору, который выдаёт 0. В этот момент третий (тактовый) транзистор блокирует сигнал.

В следующей тактовой фазе сигнал генератора тактовых импульсов становится высоким, благодаря чему сигнал 0 достигает второго инвертора, который выдаёт 1. Поскольку сигнал «удержание» высокий, сигнал возвращается назад, но блокируется транзистором генератора тактовых импульсов. Динамическим эту цепь делает то, что в данный момент на первый инвертор не поступает входящих сигналов. Его вход остаётся 1 (показано серым) из-за имеющейся у цепи ёмкости. Когда-нибудь этот заряд утечёт, значение потеряется, но до этого момента произойдёт новое переключение генератора тактовых импульсов.

После переключения состояния генератора тактовых импульсов вход на второй инвертор обеспечит ёмкость цепи (см. ниже). Сигнал возвращается назад, перезаряжая и обновляя вход на первый инвертор. При последующих переключениях тактовой частоты защёлка будет переключаться между этой и предыдущей диаграммой, сохраняя хранящееся в ней значение и поддерживая выходной сигнал в стабильном состоянии.

Ключом к работе защёлки служит наличие двух инверторов, поддерживающих выходной сигнал в стабильном состоянии. Нечётное количество инверторов вызвало бы осцилляции – эта особенность используется генератором подкачки заряда 8086. Также пары инверторов использует набор регистров 8086 для хранения битов. Однако в наборе регистров два инвертора соединены напрямую, без проходных транзисторов, управляемых генератором тактовых импульсов, что даёт более компактную, но трудную в управлении систему хранения.

Когда сигнал тактовой частоты высокий, значение проходит через первый инвертор.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

JK-триггер

Символ JK-триггера с дополнительными асинхронными входами S и R, аналогично представлению в среде разработки

| J | K | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К [5] .

См. также

Полезное

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные: move , input , outptut , load и store .

- Команды перехода: goto , if . goto , call и return .

- Команда останова: halt .

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Примечания

D-триггеры

D-триггер («прозрачный триггер», «защелка», latch) относится к категории синхронных устройств, тактируемых по входу С. Также имеется вход для данных D (Data). По функциональным возможностям устройство относится к триггерам с приёмом информации по одному входу.

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

Прозрачность D-триггера не всегда является полезным свойством. Чтобы её избежать, применяются двойные элементы (flip-flop, «хлопающий» триггер), они обозначаются литерами TT. Первым триггером служит обычная защёлка, пропускающая входной сигнал на выход. Второй триггер служит элементом памяти. Тактируются оба устройства одним стробом.

Литература

- Жан М. Рабаи, Ананта Чандракасан, Боривож Николич Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-ое изд. — М.: «Вильямс», 2007. — С. 912. — ISBN 0-13-090996-3

- Шамшин В.Г., История технических средств коммуникации. Учеб. пособие., 2003. Дальневосточный Государственный Технический Университет. 3.1 Триггеры Часть 1. Электронная схема и формальные модели 4.5. Триггер. 5.7. Что такое триггер? Логические основы ЭВМ. D-Триггер 5. ТРИГГЕРЫ 2.3.1. Триггеры RS-триггер Триггеры Триггер 1.6. Триггеры Триггеры 9.2.5. ПОСТРОЕНИЕ ЭЛЕМЕНТОВ ПАМЯТИ КМОП-триггер Шмитта 3. Триггеры Асинхронный RS-триггер RS-ТРИГГЕР Константин Рыжов - 100 великих изобретений. 1919 г. - Триггер Бонч-Бруевича, Икклза и Джордана.

Wikimedia Foundation . 2010 .

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Заключение

8086 активно использует динамические защёлки для хранения внутренних состояний. Их видно под микроскопом, и их цепи можно отследить и понять. Кристалл 8086 интересно анализировать, поскольку, в отличие от современных процессоров, его транзисторы достаточно крупные, чтобы их было видно под микроскопом. Для своего времени это был сложный процессор с 29 000 транзисторами, однако всё же достаточно простой для того, чтобы его цепи можно было отследить и понять.

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Из чего состоит оперативная память?

Теперь вернемся к нашей памяти, она представляет собой большую группу регистров, которые хранят данные. Существует SRAM (статическая память) и DRAM (динамическая память). В статической памяти регистры представлены в виде триггеров, а в динамический в виде конденсаторов, которые со временем могут терять заряд. Сегодня в ОЗУ используется именно DRAM, где каждая ячейка — это транзистор и конденсатор, который при отсутствии питания теряет все данные. Именно поэтому, когда мы отключаем компьютер, оперативная память очищается. Все драйвера и другие важные программы компьютер в выключенном состоянии хранит на SSD, а уже при включении он заносит необходимые данные в оперативную память.

Вам наверняка будет интересно узнать виды оперативной памяти. На эту тему у нас есть отличный материал

Ячейка динамической оперативной памяти, как уже было сказано выше, состоит из конденсатора и транзистора, хранит она 1 бит информации. Точнее, саму информацию хранит конденсатор, а за переключения состояния отвечает транзистор. Конденсатор мы можем представить в виде небольшого ведерка, который наполняется электронами при подаче тока. Подробнее работу динамической оперативной памяти мы рассмотрели еще 7 лет назад. С тех пор мало что изменилось в принципах её работы. Если конденсатор заполнен электронами, его состояние равно единице, то есть на выходе имеем 1 бит информации. Если же нет, то нулю.

Ссылки

Как работает процессор?

Нельзя говорить о памяти, не сказав пару слов о процессоре. Процессор и оперативной память довольно похожи, так как в обоих случаях используются логические устройства, которые могут принимать лишь два состояния. Однако процессор выполняет задачи, связанные с вычислениями. Для этого у него имеется устройство управления — именно на него поступают наши инструкции, арифметико-логическое устройство — оно отвечает за все арифметические операции (сложение, вычитание и так далее) и регистры.

Помимо оперативной памяти, в компьютере имеется кэш-память. Если вам интересна эта тема, можете изучить наш недавний материал.

Так как инструкции, поступающие на процессор, работают с данными из памяти, эти данные нужно где-то хранить. Брать их постоянно из оперативной памяти — слишком долго, поэтому в процессоре имеется своя память, представленная в виде нескольких регистров — она является самой быстрой памятью в компьютере.

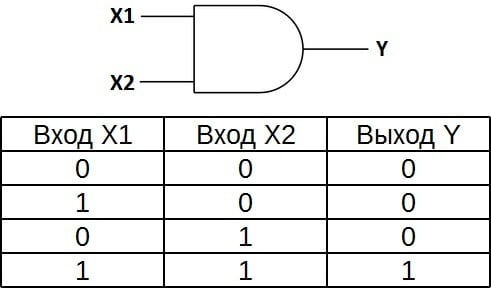

Что такое регистр? Регистр в процессоре представлен в виде триггера, который может хранить 1 бит информации. Триггер — это один из множества логических элементов в микрочипах. Благодаря своей логике он способен хранить информацию. Вот так выглядит D-триггер:

Это D-триггер и он способен хранить информацию. Каждое простейшее логическое устройство, включая D-триггер, состоит из логических операций. На фото выше можно заметить знак «&» — это логическое И

Таблица истинности для логического «И»

Верхний переключатель «D» в D-триггере меняет значение бита, а нижний «C» включает или отключает его хранение. Вам наверняка интересно, как устроен этот «D-триггер». Подробнее работу триггеров вы можете изучить по видеоролику ниже:

Помимо D-триггера, существуют также RS-триггер, JK-триггер и другие. Этой теме посвящена не одна книга, можете изучить логические устройства микрочипов самостоятельно. Было бы неплохо углубиться еще и в тему квантовых процессоров, потому что очевидно, что будущее именно за ними.

Реализация в кремнии

8086 и другие процессоры той эры создавались на основе транзисторов типа N-МОП. Они изготавливались из кремниевой подложки, к которой в процессе легирования добавлялись примеси мышьяка или бора, формировавшие транзисторы. Сверху кремния находился поликремний, создававший затворы транзисторов и проводники, связывавшие все компоненты между собой. Ещё один слой, металлический, обеспечивал дополнительные токопроводящие связи. Современные процессоры, для сравнения, используют технологию КМОП, комбинирующую технологии N-МОП и P-МОП, а металлических проводящих слоёв у них больше одного.

Как в ИС реализуется N-МОП транзистор (МОП-структура)

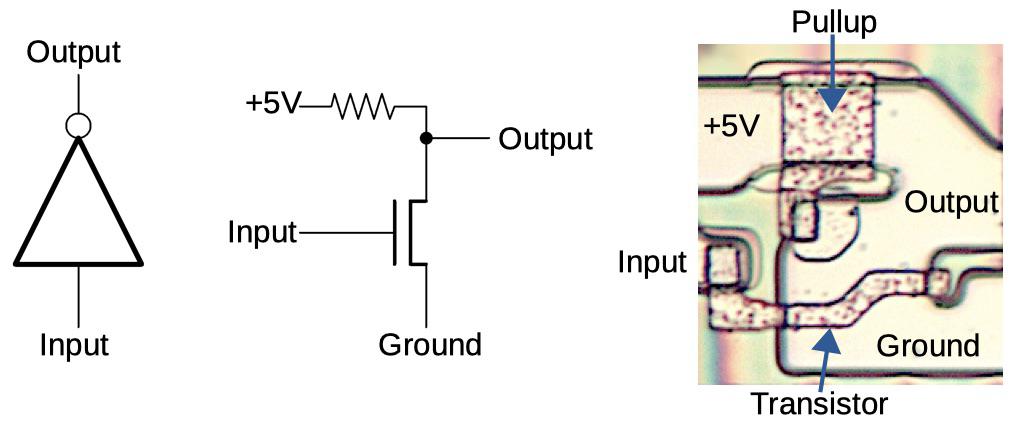

На диаграмме выше показана структура транзистора. Транзистор можно считать выключателем, позволяющим току протекать от одного участка (исток) к другому (сток). Транзистор управляется затвором, сделанным из кремния особого типа – поликремния. Подача напряжения на затвор позволяет току течь между истоком и стоком, а подтягивание затвора к 0 В блокирует ток. От кремния затвор отделён изолирующим слоем оксида – из-за этого затвор работает как конденсатор, что видно на примере динамической защёлки.

Инвертор (ниже) сделан из N-МОП транзистора и резистора. При низком сигнале транзистор отключён, поэтому подтягивающий резистор подтягивает выходной сигнал наверх. При высоком сигнале транзистор включается, соединяя выход с землёй и подтягивая выход вниз. Таким образом цепь инвертирует входящий сигнал.

Подтягивающий резистор в N-МОП затворе реализуется при помощи транзистора особого типа. Транзистор с собственным каналом [depletion-mode transistor] работает как резистор, но занимает меньше места и имеет большую эффективность.

На схеме показано, как из транзистора и резистора получается инвертор. На фото видно, как схема реализована на чипе. Металлический слой удалён, чтобы было видно поликремний и кремний.

На фото справа показано, как в 8086 физически реализован инвертор. Желтоватые участки – это токопроводящий кремний с примесями, а пятнистые – это поликремний сверху. Транзистор получается там, где поликремний пересекает кремний с примесью. Поликремний формирует затвор транзистора, а участки кремния с обеих сторон дают исток и сток транзистора. Большой поликремниевый прямоугольник формирует подтягивающий вверх резистор между +5 В и выходом. Можно сопоставить строение этих физических структур со схемой.

На диаграмме ниже показана реализация защёлки на чипе. Отмечены проходной транзистор и два инвертора; первый инвертор описан выше. Поликремниевые проводники соединяют компоненты друг с другом. Дополнительные соединения обеспечивал металлический слой (удалён для фото). Сложная форма транзисторов позволяет наиболее эффективно использовать пространство.

Микроскопическое фото защёлки в процессоре 8086. Металлический слой с проводниками удалён, однако видны его следы в виде красноватых вертикальных линий. Фото повёрнуто на 180°, чтобы соответствовать схеме.

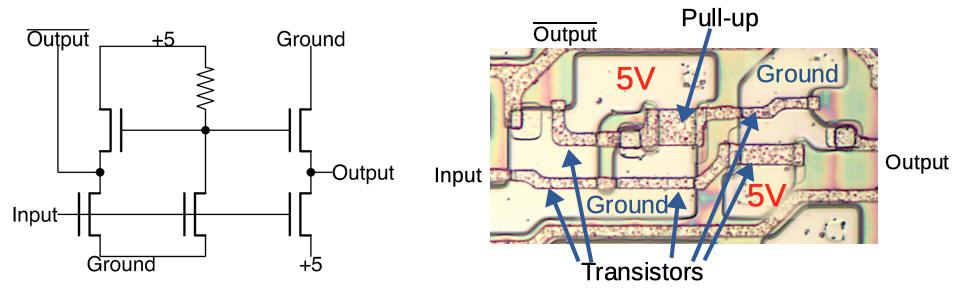

В защёлке используются выходные буферы, не отмеченные на схеме, дающие высокотоковые сигналы для выхода и инвертированного выхода. У этих буферов смешное название, «супербуферы» – потому что они выдают ток гораздо выше, чем у типичного N-МОП инвертора. Проблема N-МОП инвертора в том, что он работает медленно при управлении какой-либо цепью с высокой ёмкостью. Поскольку супербуфер даёт больший ток, он переключает сигнал гораздо быстрее. Достигает он этого, заменяя подтягивающий резистор транзистором, дающим больший ток. Минус в том, что подтягивающий транзистор требует инвертор для работы, поэтому схема супербуфера получается сложнее. Поэтому супербуфер используются только по необходимости – обычно при отправке сигнала на много затворов или при управлении длинной шиной.

Реализация супербуфера в защёлке 8086. Отметьте, что соединение с +5 В и землёй перенесены на самые правые транзисторы.

На диаграмме выше приведена схема супербуфера в защёлке 8086. В отличие от обычного супербуфера, в этом есть и инвертирующий, и не инвертирующий супербуфер. Чтобы разобраться в схеме, отметьте, что центральный резистор и транзистор формируют инвертор. Выход инвертора соединяется с верхними транзисторами, а не инвертированный вход соединяется с нижними транзисторами. Тогда, если вход 1, включаются нижние транзисторы, а если вход 0, то благодаря инвертору включаются верхние транзисторы. Тогда, если вход 1, нижние транзисторы притянут выход вверх, а соответствующий ему выход – вниз. Если вход 0, тогда верхние транзисторы притянут выход вниз, а соответствующий ему выход – вверх.

Проблема N-МОП инвертора в том, что у подтягивающего вверх резистора ток ограничен. Когда на выходе 0, транзистор в инверторе быстро и с относительно большим током подтягивает выход вниз. Однако если на выходе 1, выход подтягивается наверх гораздо более слабым подтягивающим резистором.

Супербуфер похож на КМОП-инвертор, поскольку у него есть подтягивающий вверх транзистор и подтягивающий вниз транзистор. Разница в том, что КМОП использует транзисторы типов P-МОП и N-МОП, а у P-МОП транзистора инвертированный вход затвора. И наоборот, для супербуфера N-МОП требуется отдельный инвертор. Иначе говоря, КМОП инвертор использует два транзистора, а эффективность у супербуфера гораздо меньше, поскольку ему требуется четыре транзистора.

Супербуфер использует транзистор с собственным каналом для подтягивания вверх и транзистор с индуцированным каналом [enhancement mode transistor] для подтягивания вниз. Пороговое напряжение транзистора с собственным каналом ниже нуля, что позволяет подтягивать его выход до 5 В, и не отключаться при менее высоком напряжении. Когда выход низкий, транзистор с собственным каналом всё ещё будет включён, и будет работать как обычный подтягивающий вверх в обычном инверторе, поэтому через него будет течь определённый ток. Подробнее о супербуфере можно почитать по ссылке.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

- LOAD_A 8 . Это команда сохраняет в ОЗУ данные, скажем, . Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкцию load_A — поместить данные 1000 (последние 4 бита команды) в регистр A .

- LOAD_B 2 . Ситуация, аналогичная прошлой. Здесь помещается число 2 ( 0010 ) в регистр B .

- ADD B A . Команда суммирует два числа (точнее прибавляет значение регистра B в регистр A ). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистр A .

- STORE_A 23 . Сохраняем значение регистра A в ячейку памяти с адресом 23 .

Вот такие операции нужны, чтобы сложить два числа.

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

RS-триггеры

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

RS-триггер, или SR-триггер

| S | R | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | * |

| 1 | 1 | 1 | * |

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от англ. Set - установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset - сбросить) выходное состояние становится равным логическому нулю. Если RS-триггер синхронный, то состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, является запрещённым. Так, например, схема RS-триггера, изображённая на рисунке, при подаче на оба инверсных входа логического нуля перейдёт в состояние, когда на обоих выходах будут единицы, что не соответствует логике выхода триггера, поскольку инверсный выход будет равен неинверсному , т.е. .

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени.

D-триггер

D-триггер (D от англ. delay - задержка) - запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

T-триггер

Работа схемы T-триггера (при T=1) на базе восьми 2И-НЕ логических вентилей. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение , то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

Смотреть что такое "Триггер (электроника)" в других словарях:

Триггер (значения) — Триггер (англ. trigger в значении существительного «собачка, защёлка, спусковой крючок в общем смысле, приводящий нечто в действие элемент»; в значении глагола «приводить в действие»): в русском языке первоначально термин из области… … Википедия

ТРИГГЕР — в э к с п е р и м е н т а л ь н о й я д е р н о й ф и з ик е и ф и з и к е э л е м е н т а р н ы х ч а с т и ц иерархия последовательных решений о соответствии признаков события изучаемому явлению (ядерной реакции, актам рассеяния и распада… … Физическая энциклопедия

Триггер — У этого термина существуют и другие значения, см. Триггер (значения). Триггер (триггерная система) класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под… … Википедия

Электроника (наука) — Электроника раздел электротехники, наука об использовании электрических устройств, которые работают на основе управления потоками электронов или других заряженных частиц в таких устройствах, как электронные лампы или полупроводниковые приборы. В… … Википедия

SR-триггер — Запрос «Триггер» перенаправляется сюда. Cм. также другие значения. Триггер простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под… … Википедия

T-триггер — Запрос «Триггер» перенаправляется сюда. Cм. также другие значения. Триггер простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под… … Википедия

Двоичный триггер — Запрос «Триггер» перенаправляется сюда. Cм. также другие значения. Триггер простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под… … Википедия

Троичный триггер — Возможно, эта статья содержит оригинальное исследование. Добавьте ссылки на источники, в противном случае она может быть выставлена на удаление. Дополнительные сведения могут быть на странице обсуждения. (11 мая 2011) … Википедия

оптический триггер — Оптический квантовый генератор с двумя устойчивыми положениями равновесия. [Сборник рекомендуемых терминов. Выпуск 75. Квантовая электроника. Академия наук СССР. Комитет научно технической терминологии. 1984 г.] Тематики квантовая электроника… … Справочник технического переводчика

Счётчик (электроника) — У этого термина существуют и другие значения, см. Счётчик. Двухразрядный двоичный асинхронный суммирующий счётчик с последовательной организацией переноса на JK триггерах … Википедия

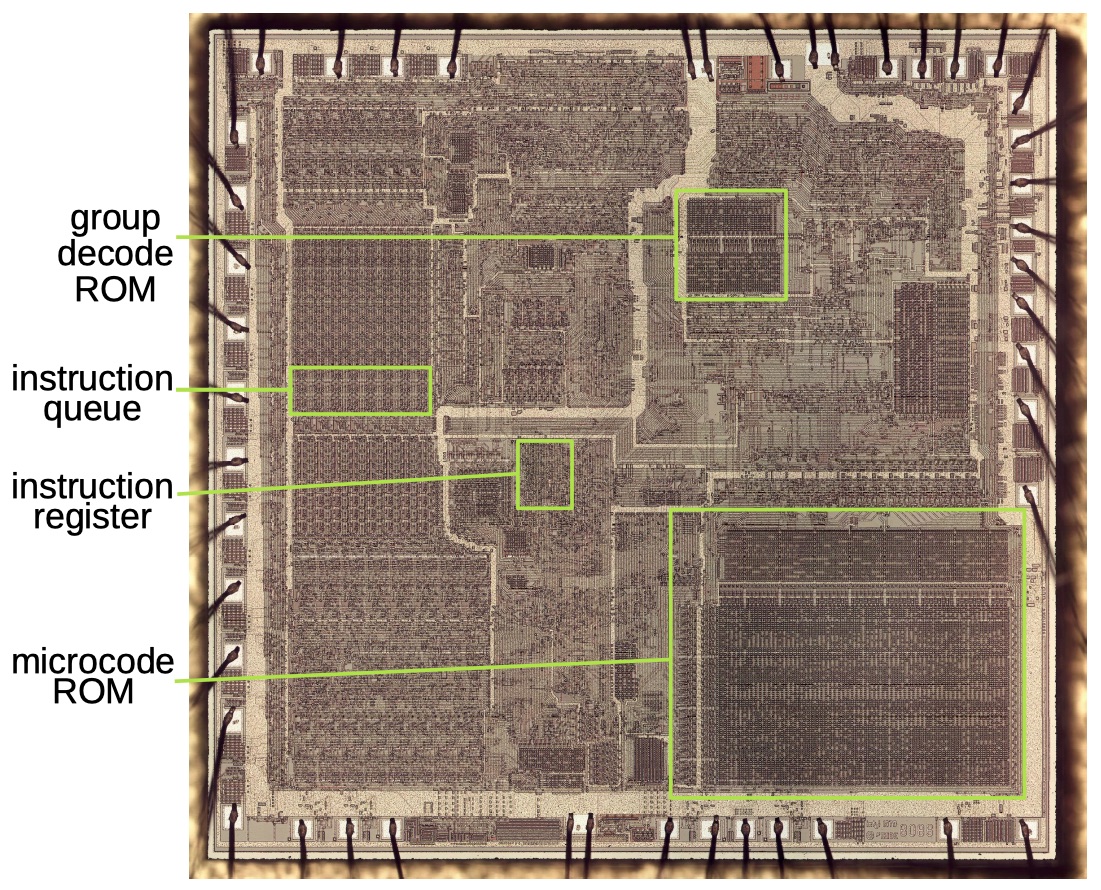

Микропроцессор Intel 8086 – один из самых влиятельных чипов. Порождённая им архитектура х86 и по сей день доминирует среди настольных и серверных компьютеров. И всё же этот чип ещё достаточно прост для того, чтобы его цепи можно было изучать под микроскопом и разбираться в них. В этой статье я объясню реализацию динамической защёлки [одноступенчатый триггер] – схемы, удерживающей один бит. В 8086 есть более 80 защёлок, разбросанных по всему чипу, и удерживающих различные важные биты статуса процессора, но я сконцентрируюсь на восьми из них, реализующих регистр команд и хранящих выполняющуюся команду.

Как компьютер запоминает данные в ОЗУ?

Последовательность битов или 1 байт «01000001», записанный в ОЗУ, может означать что угодно — это может быть число «65», буква «А» или цвет картинки. Чтобы операционная система могла понимать, что означают эти биты, были придуманы различные кодировки для разных типов данных: MP3, WAV, MPEG4, ASCII, Unicode, BMP, Jpeg. Например, давайте попытаемся записать кириллическую букву «р» в нашу память. Для этого сначала необходимо перевести её в формат Unicode-символа (шестнадцатеричное число). «р» в Unicode-таблице это «0440». Далее мы должны выбрать, в какой кодировке будем сохранять число, пусть это будет UTF-16. Тогда в двоичной системе Unicode-символ примет вид «00000100 01000000». И уже это значение мы можем записывать в ОЗУ. Оно состоит из двух байт. А вот если бы мы взяли английскую «s», в двоичном виде она бы выглядела вот так «01110011».

Дело в том, что английский алфавит занимает лишь 1 байт, так как в UTF-кодировке он умещается в диапазон чисел от 0 до 255. В 256 комбинаций спокойно вмещаются числа от 0 до 9 и английский алфавит, а вот остальные символы уже нет, поэтому, например, для русских символов нужно 2 байта, а для японских или китайских символов нам понадобится уже 3 и даже 4 байта.

Вот мы и разобрались с тем, как работает оперативная память и как можно записать в неё данные. Понравился материал? Делитесь им с друзьями и давайте обсудим его в нашем чате.

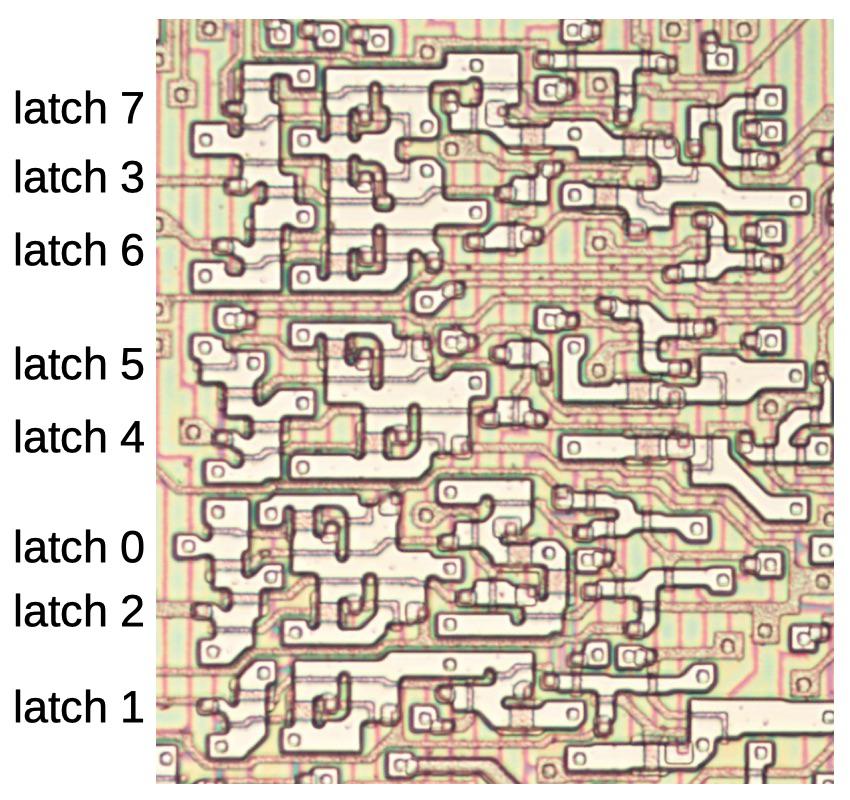

Регистр команд

Как и большинства процессоров, у 8086 есть регистр команд, где хранится текущая выполняемая команда. В 8086 регистр команд хранит первый байт команды (которая может состоять из нескольких байт), поэтому он сделан из восьми защёлок. Можно было бы подумать, что они будут идентичными, однако каждая из них имеет свою форму. Схема расположения элементов процессора 8086 высоко оптимизирована, поэтому форма каждой защёлки сделана такой, чтобы наилучшим образом использовать доступное пространство из-за ограничений окружающих её проводников. В частности отметьте, что некоторые защёлки соединяются вместе, и имеют общее питание и землю. Видимо, по той же причине защёлки идут не подряд.

Все 8 защёлок несколько разной формы, оптимизированной с учётом окружающих проводников. Ранее в статье описывалась защёлка №1, повёрнутая на 180°. Красные вертикальные линии – следы удалённого слоя металла.

Команда путешествует по 8086 извилистым путём. Процессор использует увеличивающую быстродействие предварительную выборку, загружая команды из памяти перед тем, как они потребуются. Они хранятся в очереди команд, 6-байтной очереди, расположенной в середине набора регистров. У современных процессоров, для сравнения, командный кэш может достигать размера нескольких мегабайт.

При выполнении команды она сохраняется в регистре команд, примерно в центре чипа. Относительно большие расстояния и объясняют необходимость использования супербуфера. Регистр команд скармливает команду в «ПЗУ групповой расшифровки». Это ПЗУ определяет высокоуровневые характеристики команды – однобайтовая она, или многобайтовая, или это префикс команды. И это лишь небольшая часть сложной системы обработки команд 8086. Другие защёлки хранят части команд, отмечая использования регистра и операции АЛУ, а отдельная цепь управляет движком микрокода – но это я буду описывать отдельно.

Кристалл 8086, отмечены ключевые компоненты для обработки команд. По периметру распаечные провода соединяют кристалл с внешними контактами.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Читайте также: