Какой компанией был изготовлен первый процессор sparc

Масштабируемая процессорная архитектура SPARC (Scalable Processor Architecture) компании Sun Microsystems является наиболее широко распространенной RISC-архитектурой, отражающей доминирующее положение компании на рынке UNIX рабочих станций и серверов. Процессоры с архитектурой SPARC лицензированы и изготавливаются по спецификациям Sun несколькими производителями, среди которых следует отметить компании Texas Instruments, Fujitsu, LSI Logic, Bipolar International Technology, Philips, Cypress Semiconductor и Ross Technologies. Эти компании осуществляют поставки процессоров SPARC не только самой Sun Microsystems, но и другим известным производителям вычислительных систем, например, Solbourne, Toshiba, Matsushita, Tatung и Cray Research.

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора. В последствии, по мере улучшения технологии изготовления интегральных схем, она постепенно развивалось и в настоящее время имеется 64-битовая версия этой архитектуры (SPARC-V9), которая положена в основу новых микропроцессоров, получивших название UltraSPARC.

Первый процессор SPARC был изготовлен компанией Fujitsu на базе вентильной матрицы, работающей на частоте 16.67 МГц. На основе этого процессора была разработана первая рабочая станция Sun-4 с производительностью 10 MIPS, объявленная осенью 1987 года (до этого времени компания Sun использовала в своих изделиях микропроцессоры Motorola 680X0). В марте 1988 года Fujitsu увеличила тактовую частоту до 25 МГц создав процессор с производительностью 15 MIPS.

Позднее компания Sun умело использовала конкуренцию среди компаний-поставщиков интегральных схем, выбирая наиболее удачные разработки для реализации своих изделий SPARCstation 1, 1+, IPC, ELC, IPX, 2 и серверов серий 4xx и 6xx. Тактовая частота процессоров SPARC была повышена до 40 МГц, а производительность - до 28 MIPS.

Дальнейшее увеличение производительности процессоров с архитектурой SPARC было достигнуто за счет реализации в кристаллах принципов суперскалярной обработки компаниями Texas Instruments и Cypress. Процессор SuperSPARC компании Texas Instruments стал основой серии рабочих станций и серверов SPARCstation/SPARCserver 10 и 20. В зависимости от смеси команд он обеспечивает выдачу до трех команд за один машинный такт. Процессор SuperSPARC имеет сбалансированную производительность на операциях с фиксированной и плавающей точкой. Он имеет внутренний кэш емкостью 36 Кб (20 Кб - кэш команд и 16 Кб - кэш данных), раздельные конвейеры целочисленной и вещественной арифметики и при тактовой частоте 75 МГц обеспечивает производительность около 205 MIPS.

Компания Texas Instruments разработала также 50 МГц процессор MicroSPARC с встроенным кэшем емкостью 6 Кб, который ранее широко использовался в дешевых моделях рабочих станций SPARCclassic и LX. Затем Sun совместно с Fujitsu создали новую версию кристалла MicroSPARC II с встроенным кэшем емкостью 24 Кб. На его основе построены рабочие станции и серверы SPARCstation/SPARCserver 4 и 5, работающие на частоте 70, 85 и 110 МГц.

Хотя архитектура SPARC в течение длительного времени оставалась доминирующей на рынке процессоров RISC, особенно в секторе рабочих станций, повышение тактовой частоты процессоров в 1992-1994 годах происходило более медленными темпами по сравнению с повышением тактовой частоты конкурирующих архитектур процессоров. Чтобы ликвидировать это отставание, а также в ответ на появление на рынке 64-битовых процессоров компания Sun разработала и проводит в жизнь пятилетнюю программу модернизации. В соответствии с этой программой Sun планировала довести тактовую частоту процессоров MicroSPARC до 100 МГц в 1994 году (процессор MicroSPARC II с тактовой частотой 110 МГц используется в рабочих станциях и серверах SPARCstation 4 и 5). В конце 1994 и в течение 1995 года на рынке появились микропроцессоры hyperSPARC и однопроцессорные и многопроцессорные рабочие станции SPARCstation 20 с тактовой частотой процессора 100, 125 и 150 МГц. К середине 1995 года тактовая частота процессоров SuperSPARC была доведена до 85 МГц (60, 75 и 85 МГц версии этого процессора в настоящее время применяются в рабочих станциях и серверах SPARCstation 20, SPARCserver 1000 и SPARCcenter 2000 компании Sun и 64-процессорном сервере компании Cray Research). Наконец, в ноябре 1995 года, появились 64-битовые процессоры UltraSPARC-I с тактовой частотой 143, 167 и 200 МГц, и были объявлены процессоры UltraSPARC-II с тактовой частотой от 250 до 300 МГц, серийное производство которых должно начаться в середине 1996 года. В дальнейшем планируется выпуск процессоров UltraSPARC-III с частотой до 500 МГц.

Таким образом, компания Sun Microsystems в настоящее время обладает широчайшим спектром процессоров, способных удовлетворить нужды практически любого пользователя, как с точки зрения производительности выпускаемых ею рабочих станций и серверов, так и в отношении их стоимости, и судя по всему не собирается уступать своих позиций на быстро меняющемся компьютерном рынке.

Масштабируемая процессорная архитектура SPARC (Scalable Processor Architecture) разработана компанией Sun Microsystems в 1986 году. Архитектура SPARC – это архитектура системы команд центрального процессора, полученная на основе понятия о вычислительной машине с ограниченным набором команд RISC (Restricted (Reduced) Instruction Set Computer). Микропроцессоры архитектуры SPARC лицензированы и изготавливаются по спецификациям Sun несколькими производителями, в том числе ЗАО «МЦСТ».

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора и получила название SPARC V7. Она обладала всеми чертами классических RISC процессоров, сочетая простоту набора команд и высокую скорость исполнения кода. Впоследствии, по мере улучшения технологии изготовления интегральных схем, она постепенно развивалась и в 1990 году опубликована спецификация SPARC V8, а затем, в 1993 году – 64-битовая версия архитектуры (SPARC V9), положенная в основу новых микропроцессоров, получивших название UltraSPARC.

Процессоры архитектуры SPARC V8 (МЦСТ R150 и МЦСТ R500 ) – первые продукты ЗАО «МЦСТ». Благодаря надёжности, стабильной производительности и умеренному энергопотреблению они хорошо зарекомендовали себя в различных управляющих комплексах.

В настоящее время завершена разработка микропроцессора МЦСТ R1000, совместимого с архитектурой SPARC V9. Характеристики R1000 допускают его применение как в системах управления, так и при решении задач обработки данных.

Рассмотрим основные свойства архитектуры SPARC на примере микропроцессора МЦСТ R500. В соответствии со спецификацией SPARC V8 микропроцессор характеризуется следующими свойствами:

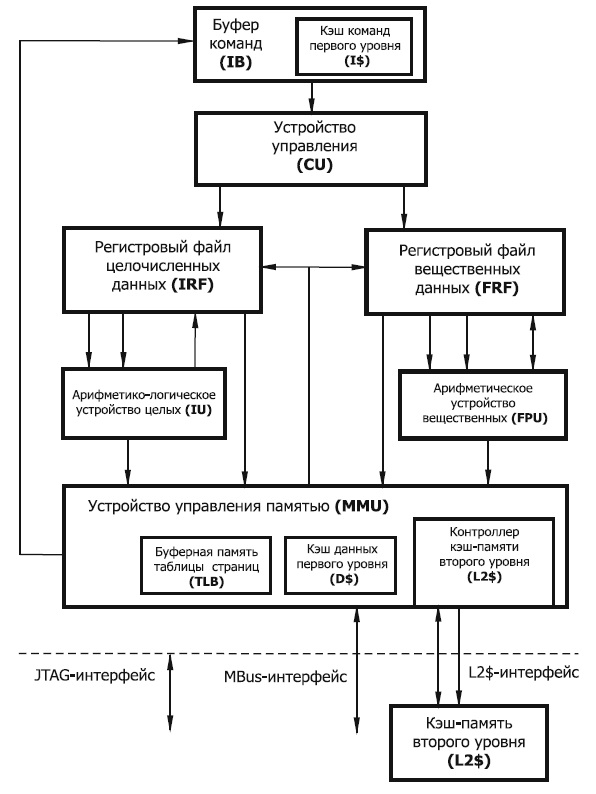

Рассмотрим структуру ядра процессора МЦСТ R500 , приведённую на рисунке 1, и основные функции элементов ядра.

Рисунок 1 – Структура ядра микропроцессора МЦСТ R500

Буфер команд (IB). Данный модуль предназначен для выдачи запросов на получение команд в устройство управления памятью, приёма, промежуточного хранения и выдачи команд в устройство управления. Одним из основных компонентов буфера команд является кэш-память команд первого уровня.

Кэш команд первого уровня (I$). Кэш-память – высокоскоростная память небольшого объёма с низкой задержкой доступа, предназначенная для ускорения обращения к часто используемым блокам основной оперативной памяти. Ёмкость кэша I$ составляет 16 Кбайт. В кэш команд входит три блока памяти: память данных, память тегов и память механизма старения. Механизм старения определяет, какие блоки в памяти данных могут быть замещены. Кэш I$ встроен в ядро и находится на том же кристалле.

Устройство управления (CU) предназначено для решения следующих задач:

- дешифрирование поступающих из кэша команд I$ инструкций;

- формирование пусков и блокировки устройств;

- организация чтения операндов из целочисленного IRF и вещественного FRF регистровых файлов для соответствующих арифметико-логических устройств (АЛУ) и записи результатов в соответствующие регистровые файлы;

- управление байпасами устройства целочисленных команд.

Байпас (англ. bypass – обход) – функция в электронном устройстве, позволяющая выполнить коммутацию входного сигнала непосредственно на выход, минуя все функциональные блоки. При проектировании суперскалярных процессоров байпасы применяют для сокращения количества блокировок вычислительного конвейера (см. ниже), обходя избыточные элементы на пути доставки данных. Если выход одной из стадий конвейера требуется на вход другой стадии, данные передаются через байпас-шину. Без байпасов данные пришлось бы записывать и считывать из регистрового файла. Это может потребовать исполнения дополнительных стадий конвейера и вызовет замедление.

Устройство CU содержит регистры состояния процессора и организует их запись, чтение и модификацию. Кроме того, оно управляет обработкой программных и аппаратных исключительных ситуаций и внешних прерываний.

Регистровый файл – модуль микропроцессора, реализующий его регистры в виде массива запоминающих ячеек. В ядре процессора R500 находятся 2 регистровых файла: для целочисленных данных и для вещественных данных.

Регистровый файл целочисленных данных (IRF). В IRF хранятся данные целочисленного типа для проведения с ними операций. Регистровый файл содержит 136 регистров по 32 бита (8 окон по 16 регистров и 1 окно из 8 глобальных регистров).

Регистровый файл вещественных данных (FRF). В этом модуле хранятся данные вещественного типа. Регистровый файл FRF содержит 32 регистра 32-разрядных данных. При этом модуль может трактоваться в программах как набор из 32 регистров одинарного формата (разрядность 32 бита), либо как 16 регистров двойного формата (разрядность 64 бита), либо как смешанный набор регистров первого и второго вида.

Арифметико-логическое устройство целочисленных команд (IU) предназначено для выполнения команд целочисленного сложения/вычитания, логических команд, команд сдвига, а также вычисления адреса в командах обращения к памяти и передачи управления.

Арифметико-логическое устройство вещественных команд (FPU) предназначено для выполнения команд с операциями над вещественными числами, а также команд умножения и деления целых чисел.

Устройство управления памятью (MMU) выполняет следующие функции:

- Определяет множество адресных контекстов, которые соответствуют программным процессам. Адресный контекст процесса включает в себя содержимое выделенного процессу адресного пространства задачи, а также содержимое относящихся к процессу аппаратных регистров и структур данных ядра. Адреса в адресных контекстах уникальны.

- Преобразует 32-разрядные виртуальные адреса активных процессов в 36-разрядные физические адреса оперативной памяти. Соответствие виртуальной памяти физической обеспечивается для страниц размером 4 Кбайт, сегментов размером 256 Кбайт, областей размером 16 Мбайт и контекстов размером 4 Гбайт.

- Задаёт совместное использование памяти. Области адресных пространств для пар контекстов могут быть установлены разделяемыми с точностью до страницы.

- Организует защиту памяти. Доступ к адресуемой памяти назначается с установкой ограничений. Каждому контексту можно индивидуально разрешить доступ к страницам по чтению, записи или выполнению.

- Обеспечивает (при программной поддержке со стороны операционной системы) механизм подкачки отсутствующих в основной памяти страниц из внешней памяти.

- Обеспечивает поддержку обращений операционной системы к другим контекстам в специальных режимах и режимах защиты.

В устройство MMU входят кэш таблицы страниц TLB (Table Lookaside Buffer), кэш данных первого уровня D$ (Data Cache) и контроллер кэш-памяти второго уровня L2$ (L2$ controller).

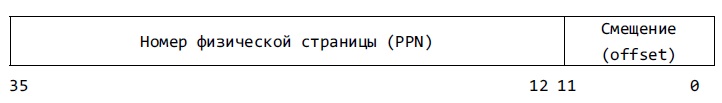

Физические адреса состоят из номера физической страницы PPN (Physical Page Number) и смещения внутри страницы (offset).

Рисунок 2 – Структура физического адреса

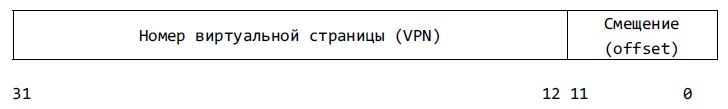

Виртуальные адреса состоят из номера виртуальной страницы VPN (Virtual Page Number) и смещения внутри страницы (offset).

Рисунок 3 – Структура виртуального адреса

Устройство управления памятью выполняет трансляцию адресов путём обращения к древовидной таблице трансляции в оперативной памяти, называемой таблицей страниц PT (Page Table). Когда трансляция установлена, MMU загружает строку таблицы страниц в свой кэш таблицы страниц TLB, чтобы можно было избежать обращения в память к PT при последующих обращениях. Виртуальные адреса, хранимые в кэше TLB, помечаются 16-разрядным номером контекста.

Для оптимизации размещения таблиц страниц в оперативной памяти преобразование адресов выполняется с помощью 4-уровневых таблиц страниц. Такая структура обеспечивает отображение памяти для страниц размером 4 Кбайт.

В микропроцессоре МЦСТ R500 реализован принцип конвейерного выполнения команд. Количество стадий конвейера зависит от типа выполняемой операции.

Команды над целочисленными операндами (целые команды) имеют 5-стадийный конвейер выполнения:

- F (Fetch) – выборка команды из кэша команд I$;

- D (Decode) – дешифрация (декодирование) команды и чтение операндов из регистрового файла целых IRF;

- E (Execute) – выполнение целой команды в АЛУ целых IU;

- C (Cache) – запись результата целой команды в буферный регистр;

- W (Write) – запись результата в целый регистровый файл IRF.

Рисунок 4 – Конвейер целых команд

Конвейер выполнения вещественных команд включает семь стадий:

- F – выборка команды из кэша команд I$;

- D (Decode) – дешифрация команды;

- R (Read) – чтение операндов из вещественного регистрового файла FRF;

- E1, E2, E3 (Execute) – выполнение команды в вещественном АУ FPU;

- W (Write) – запись результата в вещественный регистровый файл FRF.

Рисунок 5 – Конвейер вещественных команд

Команды загрузки из кэш-памяти первого уровня L1$ имеют 5-стадийный конвейер выполнения

- F – выборка команды из кэша команд I$;

- D (Decode) – дешифрирование команды;

- E (Execute) – вычисление виртуального адреса и обращение в кэш данных первого уровня D$;

- C (Cache) – формирование результата команды загрузки (формирование физического адреса запроса на случай промаха в кэше данных первого уровня D$);

- W (Write) – запись результата в целый регистровый файл IRF.

Рисунок 6 – Конвейер команд загрузки из кэша данных первого уровня D$

Конвейер выполнения команды загрузки из кэш-памяти второго уровня L2$ имеет 14 стадий. Дополнительно к общим стадиям здесь имеются:

- С – формирование физического адреса запроса к кэш-памяти второго уровня L2$;

- C1 – формирование запроса в контроллере кэш-памяти второго уровня L2$;

- C2, С3 – выдача запроса в кэш-память второго уровня L2$;

- C4, С5 – доступ в кэш-память второго уровня L2$;

- C6, С7 – передача тегов и данных из кэш-памяти второго уровня L2$ в микропроцессор;

- C8 – сравнение тегов из кэш-памяти второго уровня L2$ с адресом запроса;

- C9 – формирование результата команды загрузки.

Рисунок 7 – Конвейер команд загрузки из кэш-памяти

В заключение рассмотрим основные особенности архитектуры SPARC V9, на которой реализован микропроцессор МЦСТ R1000 :

| Дизайнер | Sun Microsystems (acquired by Oracle Corporation) |

|---|---|

| Биты | 64-bit (32 → 64) |

| Представлен | 1987 (shipments) |

| Версия | V9 (1993) / OSA2015 |

| Дизайн | RISC |

| Тип | Register-Register |

| Кодирование | Fixed |

| Разветвление | Condition code |

| Порядок байтов | Bi (Big → Bi) |

| Размер страницы | 8 KiB (4 KiB → 8 KiB) |

| Расширения | VIS 1.0, 2.0, 3.0 4.0 |

| Открыто | Yes, and royalty free. |

| Регистры | |

| Общее назначение | 31 (G0 = 0; non-global registers use register windows) |

| FPU (Floating Point Unit) | 32 (usable as 32 single-precision, 32 double-precision, or 16 quad-precision) |

Содержание

Организация конвейера

В процессоре UltraSPARC реализован девятиступенчатый конвейер. Это означает, что задержка (время от начала до конца выполнения) большинства команд составляет девять тактов.

Целочисленное исполнительное устройство Главной задачей при разработке целочисленного исполнительного устройства (IEU) является обеспечение максимальной производительности при поддержке программной совместимости с существующим системным и прикладным программным обеспечением. Целочисленное исполнительное устройство UltraSPARC объединяет в себе несколько важных особенностей:

- 2 АЛУ для выполнения арифметических и логических операций, а также операций сдвига;

- Многократные целочисленные устройства умножения и деления;

- регистровый файл с восемью окнами и четырьмя наборами глобальных регистров;

- реализация цепей ускоренной пересылки результатов;

- реализация устройства завершения команд, которое обеспечивает минимальное количество цепей обхода (ускоренной пересылки данных) при построении девятиступенчатого конвейера.

Системы «Pizzabox»

| Название | Модель | Кодовое имя | Платформа | Процессоры | CPU MHz | RAM (MAX) | Начало выпуска | Конец продаж | Конец поддержки |

|---|---|---|---|---|---|---|---|---|---|

| SPARCstation 1 | 4/60 | Campus | sun4c | Fujitsu MB86901A or LSI L64801 | 20 MHz | 64 MB | 1989 | Май 1999 | |

| SPARCstation 1+ | 4/65 | Campus B | sun4c | LSI L64801 | 25 MHz | 64 MB | 1989 | Май 1999 | |

| SPARCstation 2 | 4/75 | Calvin | sun4c | Cypress CY7C601 | 40 MHz | 128 MB | 1990 | Дек 1999 | |

| SPARCstation 10 | S10 | Campus-2 | sun4m | SuperSPARC I/II или hyperSPARC | 33, 36, 40, 50, 60, 75, 80, 90, 100, 125, 150, 180, 200 MHz | 512 MB | Май 1992 | Окт 1994 | Окт 1999 |

Основные свойства архитектуры SPARC

Основные свойства архитектуры SPARC рассмотрим на примере микропроцессора МЦСТ R500:

- линейное 32-разрядное адресное пространство, т.е. пронумерованная последовательность ячеек памяти от минимального номера до максимального (0х00000000…0хFFFFFFFF – адресация до 4 Гбайт оперативной памяти);

- небольшое количество простых форматов 32-разрядных команд. Все команды в памяти выровнены по границе 32-разрядных слов. Имеется всего три базовых формата команд, в которых поля кода операции и регистровых операндов всегда находятся в одних и тех же разрядах. Доступ к памяти и ввод/вывод могут осуществляться только командами чтения/записи;

- небольшое количество способов адресации. Адрес по памяти вычисляется либо как «регистр + регистр», либо как «регистр + непосредственное значение, литерал»;

- трёхадресная регистровая команда – команды большей частью выполняют действия с двумя операндами (двумя регистрами или одним регистром и константой), помещая результат в третий регистр;

тегированные команды – команды тегированного сложения / вычитания рассматривают два младших разряда своих операндов в качестве тегов;

- команды межпроцессорной синхронизации – одна команда выполняет непрерываемую операцию «чтения и последующей записи», другая – непрерываемый «обмен содержимого регистра и памяти».

Управление интерфейсом памяти

В процессоре UltraSPARC применяется специальная подсистема ввода/вывода(MIU), которая обеспечивает управление всеми операциями ввода и вывода, осуществляемыми между локальными ресурсами: процессором, основной памятью, схемами управления и всеми внешними ресурсами системы. В частности, все транзакции, связанные с обработкой промахов кэш-памяти, прерываниями, наблюдением за когерентным состоянием кэш-памяти, операциями обратной записи и т.д., обрабатываются MIU. MIU взаимодействует с системой на частоте меньшей, чем частота UltraSPARC в соотношении 1 к 2 или 1 к 3.

Графическое устройство

Интегрированные системы с монитором

| Название | Модель | Кодовое имя | Платформа | Процессоры | Частота | RAM (MAX) | Начало выпуска | Конец продаж | Конец поддержки |

|---|---|---|---|---|---|---|---|---|---|

| SPARCstation SLC | 4/20 | Off-Campus | sun4c | Fujitsu MB86901A, LSI L64801 or LSI LSIS1C0007 | 20 MHz | 16 MB | Ноябрь 1996 | ||

| SPARCstation ELC | 4/25 | Node Warrior | sun4c | Fujitsu MB86903 or Weitek W8701 | 33 MHz | 64 MB | Окт 1998 | ||

| SPARCstation Voyager | S240 | Gypsy | sun4m | microSPARC II | 60 MHz | 80 MB | Март 1994 | Дек 1995 | Дек 2000 |

Основные критерии разработки

Чтобы сократить число потенциальных проблем, было принято несколько принципиальных решений, которые определили основные характеристики UltraSPARC:

- Реализация на кристалле раздельной кэш-памяти команд и данных;

- Организация широкой выборки команд (128 бит)

- Создание эффективных средств динамического прогнозирования направления переходов;

- Реализация девятиступенчатого конвейера, обеспечивающего выдачу для выполнения до четырех команд в каждом такте;

- Оптимизация конвейерных операций обращения к памяти

- Реализация команд обмена данными между памятью и регистрами плавающей точки, позволяющая не приостанавливать диспетчеризацию команд обработки;

- Реализация на кристалле устройства управления памятью (MMU);

- Расширение набора команд для поддержки графики и обработки изображений;

- Реализация новой архитектуры шины UPA.

Содержание

Содержание

Архитектура

Структура процессора UltraSPARC

Процессор UltraSPARC представляет собой производительный, высокоинтегрированный суперскалярный процессор, реализующий 64-битовую архитектуру SPARC-V9.В его состав входят: устройство предварительной выборки и диспетчеризации команд, целочисленное исполнительное устройство, устройство работы с вещественной арифметикой и модуль графики, устройства управления памятью, загрузки/записи и управления внешней кэш-памятью, модули управления интерфейсом памяти и кэш-памяти команд и данных. [Источники 2]

Процессоры на базе архитектуры SPARC

Позднее компания Sun умело использовала конкуренцию среди компаний-поставщиков интегральных схем, выбирая наиболее удачные разработки для реализации своих изделий SPARCstation 1, 1+, IPC, ELC, IPX, 2 и серверов серий 4xx и 6xx. Тактовая частота процессоров SPARC была повышена до 40 МГц, а производительность - до 28 MIPS.

Развитие архитектуры компанией Texas Instruments

Дальнейшее увеличение производительности процессоров с архитектурой SPARC было достигнуто за счет реализации в кристаллах принципов суперскалярной обработки компаниями Texas Instruments и Cypress. Процессор SuperSPARC компании Texas Instruments стал основой серии рабочих станций и серверов SPARCstation/SPARCserver 10 и 20. В зависимости от смеси команд он обеспечивает выдачу до трех команд за один машинный такт. Процессор SuperSPARC имеет сбалансированную производительность на операциях с фиксированной и плавающей точкой. Он имеет внутренний кэш емкостью 36 Кб (20 Кб - кэш команд и 16 Кб - кэш данных), раздельные конвейеры целочисленной и вещественной арифметики и при тактовой частоте 75 МГц обеспечивает производительность около 205 MIPS.

Компания Texas Instruments разработала также 50 МГц процессор MicroSPARC с встроенным кэшем емкостью 6 Кб, который ранее широко использовался в дешевых моделях рабочих станций SPARCclassic и LX. Затем Sun совместно с Fujitsu создали новую версию кристалла MicroSPARC II с встроенным кэшем емкостью 24 Кб. На его основе построены рабочие станции и серверы SPARCstation/SPARCserver 4 и 5, работающие на частоте 70, 85 и 110 МГц.

Дальнейшее развитие архитектуры SPARC

Хотя архитектура SPARC в течение длительного времени оставалась доминирующей на рынке процессоров RISC, особенно в секторе рабочих станций, повышение тактовой частоты процессоров в 1992-1994 годах происходило более медленными темпами по сравнению с повышением тактовой частоты конкурирующих архитектур процессоров. Чтобы ликвидировать это отставание, а также в ответ на появление на рынке 64-битовых процессоров компания Sun разработала и проводит в жизнь пятилетнюю программу модернизации. В соответствии с этой программой Sun планировала довести тактовую частоту процессоров MicroSPARC до 100 МГц в 1994 году (процессор MicroSPARC II с тактовой частотой 110 МГц используется в рабочих станциях и серверах SPARCstation 4 и 5). В конце 1994 и в течение 1995 года на рынке появились микропроцессоры hyperSPARC и однопроцессорные и многопроцессорные рабочие станции SPARCstation 20 с тактовой частотой процессора 100, 125 и 150 МГц. К середине 1995 года тактовая частота процессоров SuperSPARC была доведена до 85 МГц (60, 75 и 85 МГц версии этого процессора в настоящее время применяются в рабочих станциях и серверах SPARCstation 20, SPARCserver 1000 и SPARCcenter 2000 компании Sun и 64-процессорном сервере компании Cray Research). Наконец, в ноябре 1995 года, появились 64-битовые процессоры UltraSPARC-I с тактовой частотой 143, 167 и 200 МГц, и были объявлены процессоры UltraSPARC-II с тактовой частотой от 250 до 300 МГц, серийное производство которых должно начаться в середине 1996 года. В дальнейшем планируется выпуск процессоров UltraSPARC-III с частотой до 500 МГц.

Процессоры Oracle SPARC обладают массой интересных свойств: в зависимости от нагрузки автоматически регулируется количество потоков, выполняемых одним ядром (от 1 до 8), а при снижении количества задействованных ядер повышается тактовая частота работающих. Аппаратно реализован ряд алгоритмов хеширования и шифрования.

Устройство управления памятью

Высокая суперскалярная производительность процессора поддерживается соответствующей скоростью поступления для обработки команд и данных. Обычно эта задача ложится на иерархию памяти системы. Устройство управления памятью процессора UltraSPARC выполняет все операции обращения к памяти, реализуя необходимые средства поддержки виртуальной памяти. Виртуальное адресное пространство задачи определяется 64-битовым виртуальным адресом, однако процессор UltraSPARC поддерживает только 44-битовое виртуальное адресное пространство. Соответствующее преобразование является функцией операционной системы.

История

Первоначально архитектура SPARC была разработана с целью упрощения реализации32-битового процессора. Впоследствии, по мере улучшения технологии изготовления интегральных схем, она постепенно развивалась, и сегодня существует 64-битоваяверсия этой архитектуры (SPARC-V9), которая положена в основу семейства новых микропроцессоров, получивших название UltraSPARC.

Первый процессор SPARC был изготовлен компанией Fujitsu на базе вентильной матрицы, работающей на частоте 16.67 МГц. На основе этого процессора была разработана первая рабочая станция Sun-4 с производительностью 10 MIPS, объявленная осенью 1987 года. До этого времени компания Sun использовала в своих изделиях микропроцессоры Motorola 680X0. В марте 1988 года Fujitsu увеличила тактовую частоту до 25 МГц, создав процессор с производительностью 15 MIPS.

Серверные системы

| Название | Модель | Кодовое имя | Платформа | Процессоры | Частота | RAM (MAX) |

|---|---|---|---|---|---|---|

| SPARCserver 330 | 4/330 | Stingray | sun4 | Cypress CY7C601 | 25 MHz | 72 MB |

| SPARCserver 370 | 4/370 | Stingray | sun4 | Cypress CY7C601 | 25 MHz | 72 MB |

| SPARCserver 390 | 4/390 | Stingray | sun4 | Cypress CY7C601 | 25 MHz | 72 MB |

| SPARCserver 470 | 4/470 | Sunray | sun4 | Cypress CY7C601 | 33 MHz | 96 MB |

| SPARCserver 490 | 4/490 | Sunray | sun4 | Cypress CY7C601 | 33 MHz | 96 MB |

| SPARCserver 630MP | S630 | Galaxy | sun4m | до 4 Cypress CY7C601 или SuperSPARC I | 40, 50, 60 MHz | 1 GB |

| SPARCserver 670MP | S670 | Galaxy | sun4m | До 4 Cypress CY7C601 или SuperSPARC I | 40, 50, 60 MHz | 1 GB |

| SPARCserver 690MP | S690 | Galaxy | sun4m | До 4 Cypress CY7C601 или SuperSPARC I | 40, 50, 60 MHz | 1 GB |

| SPARCserver 1000/1000E | S1000 | Scorpion | sun4d | До 8 SuperSPARC I/II | 40, 50, 60, 85 MHz | 2 GB |

| SPARCcenter 2000/2000E | S2000 | Dragon | sun4d | До 20 SuperSPARC I/II | 40, 50, 60, 85 MHz | 5 GB |

Многие указанные выше модели могли быть доступны в конфигурации SPARCserver и наоборот. Также примечательно, что различные конфигурации со сторонними увеличивающими производительность процессора устройствами поддерживались компанией Sun. Например 80 МГц Weitek Power up для SPARCstation 2 и IPX или Ross hyperSPARC Mbus модуль разгонявший тактовую частоту до 200 МГц.

Устройство загрузки/записи (LSu)

LSU отвечает за формирование виртуального адреса для всех команд загрузки и записи (включая атомарные операции), за доступ к кэш-памяти данных, а также за буферизацию команд загрузки в случае промаха D-кэша (в буфере загрузки) и буферизацию команд записи (в буфере записи). В каждом такте может выдаваться для выполнения одна команда загрузки и одна команда записи.

Архитектура SPARC сегодня

Архитектура SPARC не смогла закрепиться на рынке персональных и портативных компьютеров, однако компания Sun(сейчас принадлежащая Oracle Corporation) продолжает разработку и выпуск серверных решений на основе данной технологии. Согласно информации на официальном сайте продукта[1], SPARC дает серьезный рост производительности для Java приложений, надежную защиту и бесперебойную работу, также имея возможность работы в качестве "облака". Облачные технологии Oracle на основе SPARC разработаны специально для горизонтально масштабируемой облачной инфраструктуры и вертикально масштабируемых корпоративных приложений.Эти серверы спроектированы для поддержания максимальной доступности корпоративных систем, необходимых для работы самых важных приложений как локально, так и в любой облачной среде. [Источник 3]

| |

| Частота CPU: | 143 Мгц — 200 Мгц |

|---|---|

| Число ядер: | 1 |

| L1-кэш | 16 Кб |

| Инструкция | SPARC V9 |

| Предшественник | SuperSPARC II |

| Преемник | UltraSPARC II |

UltraSPARC – микропроцессор, разработанный в 1995 году компанией Sun Microsystems и произведенный Texas Instruments. Данный процессор имеет 64-битную архитектуру для поддержки набора инструкций SPARC V9 [Источники 1] .

Управление внешней кэш-памятью

Устройство управления внешней кэш-памятью (ECU С E-кэш) процессораUltraSPARC позволяет эффективно обрабатывать промахи кэш-памяти данных(D-кэша) и команд (Е-кэша). Все обращения к внешней кэш-памяти (E-кэшу) конвейеризованы, выполняются за 3 такта и осуществляют пересылку 16 байт команд или данных в каждом такте. Такая организация дает возможность эффективно планировать конвейерное выполнение программного кода, содержащего большой объем обрабатываемых данных, и минимизировать потери производительности, связанные с обработкой промахов в D-кэше. ECU позволяет наращивать объем внешней кэш-памяти от 512 Кбайт до 4 Мбайт. [Источники 3] Архитектура процессоров

Структура

Рассмотрим структуру ядра микропроцессора МЦСТ R500.

Буфер команд (IB). Данный модуль предназначен для выдачи запросов на получение команд в устройство управления памятью, приёма, промежуточного хранения и выдачи команд в устройство управления. Одним из основных компонентов буфера команд является кэш-память команд первого уровня.

Кэш команд первого уровня (I$). Кэш-память – высокоскоростная память небольшого объёма с низкой задержкой доступа, предназначенная для ускорения обращения к часто используемым блокам основной оперативной памяти. Ёмкость кэша I$ составляет 16 Кбайт. В кэш команд входит три блока памяти: память данных, память тегов и память механизма старения. Механизм старения определяет, какие блоки в памяти данных могут быть замещены. Кэш I$ встроен в ядро и находится на том же кристалле.

Устройство управления (CU) предназначено для решения следующих задач:

- дешифрирование поступающих из кэша команд I$ инструкций;

- формирование пусков и блокировки устройств;

- организация чтения операндов из целочисленного IRF и вещественного FRF регистровых файлов для соответствующих арифметико-логических устройств (АЛУ) и записи результатов в соответствующие регистровые файлы;

- управление байпасами [1] устройства целочисленных команд.

Регистровый файл – модуль микропроцессора, реализующий его регистры в виде массива запоминающих ячеек. В ядре процессора R500 находятся 2 регистровых файла: для целочисленных данных и для вещественных данных.

Регистровый файл целочисленных данных (IRF). В IRF хранятся данные целочисленного типа для проведения с ними операций. Регистровый файл содержит 136 регистров по 32 бита (8 окон по 16 регистров и 1 окно из 8 глобальных регистров).

Регистровый файл вещественных данных (FRF). В этом модуле хранятся данные вещественного типа. Регистровый файл FRF содержит 32 регистра 32-разрядных данных. При этом модуль может трактоваться в программах как набор из 32 регистров одинарного формата (разрядность 32 бита), либо как 16 регистров двойного формата (разрядность 64 бита), либо как смешанный набор регистров первого и второго вида.

Арифметико-логическое устройство целочисленных команд (IU) предназначено для выполнения команд целочисленного сложения/вычитания, логических команд, команд сдвига, а также вычисления адреса в командах обращения к памяти и передачи управления.

Арифметико-логическое устройство вещественных команд (FPU) предназначено для выполнения команд с операциями над вещественными числами, а также команд умножения и деления целых чисел.

| Создатели: | Sun Microsystems |

|---|---|

| Выпущена: | April 1989 ; 33 years ago ( 1989-04 ) |

| Состояние разработки: | Замещена линейкой Sun Ultra и Sun Enterprise |

| Платформа: | SPARC, Архитектура:Sun-4 |

| Локализация: | Английский |

| Лицензия: | Единовременная покупка прав на разработку Стоимость: 99$ |

| Веб-сайт | Oracle & Sun Microsystems |

SPARCstation, SPARCserver и SPARCcenter — продуктовые линейки рабочих станций и серверов, основанных на микропроцессорной архитектуре SPARC, разрабатывавшихся корпорацией Sun Microsystems.

Первым продуктом линейки SPARCstation была рабочая станция SPARCstation 1 (также известная как Sun 4/60), представленная в 1989 году. Серия была очень популярна и впервые представила архитектуру Sun-4c, вариант архитектуры Sun-4, прежде использовавшийся в Sun 4/260. Отчасти благодаря задержке в разработке более современных процессоров Motorola, серия SPARCstation имела значительный успех в индустрии. Последней моделью, выпущенной под брендом SPARCstation, была SPARCstation 20. В 1995 году линейка SPARCstation была замещена линейкой Sun Ultra, а серверные решения были заменены системами Sun Enterprise

Продукты SPARCstation и SPARCserver одной модели были почти идентичными системами: единственным отличием было отсутствие у «серверных» систем графической карты. [Источник 1]

История

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора и получила название SPARC V7. Она обладала всеми чертами классических RISC процессоров, сочетая простоту набора команд и высокую скорость исполнения кода. Впоследствии, по мере улучшения технологии изготовления интегральных схем, она постепенно развивалась и в 1990 году опубликована спецификация SPARC V8, а затем, в 1993 году – 64-битовая версия архитектуры (SPARC V9), положенная в основу новых микропроцессоров, получивших название UltraSPARC.

Рис. 1. Зелёным обозначены процессоры, соответствующие седьмой версии спецификации (SPARC V7), оранжевым — SPARC V8, красным — SPARC V9. Жёлтая заливка означает многоядерный чип

Кэш-память команд

Кэш-память команд (I-кэш) представляет собой двухканальную множественно-ассоциативную кэш-память емкостью 16 Кбайт. Она организована в виде 512 строк, содержащих по 32 байта данных. С каждой строкой связан соответствующий адресный тег. Команды, поступающие для записи в I-кэш проходят предварительное декодирование и записываются в кэш-память вместе с соответствующими признаками, облегчающими их последующую обработку. Окончательное декодирование команд происходит перед их записью в буфер команд.

Модели

Настольные компьютеры SPARCstation и сервера SPARCsevers одной модели являлись практически одинаковыми системами, с разницей в том что сервера как правило не имели графической карты и монитора и продавались с серверной, а не пользовательской, лицензией ОС. Например SPARCstation 20 и SPARCserver 20 имели одинаковые материнские платы, процессоры и иные комплектующие, а также имели схожий дизайн корпуса. Большинство SPARCstation и SPARCsevers поставлялись в корпусах "Pizzabox"(коробка для пиццы) и "Lunchbox"(коробка для завтрака), что отличало данные продукты от более ранних моделей компании Sun и современных конкурентов. SPARCstation 1, 2, 4, 5, 10 и 20 поставлялись в компоновке "Pizzabox". SPARCstation SLC и ELC имели встроенный монохромный монитор компании Sun, а the SPARCstation IPC, IPX, SPARCclassic, SPARCclassic X и SPARCstation LX были в корпусе "Lunchbox".

SPARCsevers заканчивающиеся на "30" и "70" поставлялись в напольном прямоугольном корпусе "deskside"

. Модели заканчивающиеся на "90" и SPARCcenter 2000 поставлялись в стоечных шкафах. SPARCserver 1000 продавался в настольном прямоугольном корпусе с возможностью монтажа в стоечный шкаф.

Более поздние версии SPARCstation, такие как SPARCstation 10 и 20, могли быть мультипроцессорными поскольку были основаны на высокоскоростном стандарте MBus от Sun. Такие системы могли работать с одним или двумя одноядерными или двухядерными процессорами установленными в MBus модули.

До старта серии SPARCserver 600MP, всем SPARCstation\server моделям присваивался модельный номер серии Sun 4. Более поздние модели получили S-префикс. Нижеперечисленные модели расположены в хронологическом порядке. "Pizzabox" - это конфигурация компьютера в плоском прямоугольном или квадратном корпусе небольшой высоты, отчего имеет сходство с коробкой для пиццы.

Системы «Lunchbox»

"Lunchbox" - конфигурация компьютера в небольшом прямоугольном, толстом корпусе, что придавало сходство с распространенной в США коробкой для завтрака.

| Название | Модель | Кодовое имя | Платформа | Процессоры | Частота | RAM (MAX) | Начало выпуска | Конец продаж | Конец поддержки |

|---|---|---|---|---|---|---|---|---|---|

| SPARCstation IPC | 4/40 | Phoenix | sun4c | Fujitsu MB86901A or LSI L64801 | 25 MHz | 48 MB | 1990 | Дек 1999 | |

| SPARCstation IPX | 4/50 | Hobbes | sun4c | Fujitsu MB86903 or Weitek W8701 | 40 MHz | 64 MB | 1991 | Май 2000 | |

| SPARCclassic | 4/15 | Sunergy | sun4m | microSPARC | 50 MHz | 128 MB | Ноябрь 1992 | Май 1995 | Май 2000 |

| SPARCstation LX | 4/30 | Sunergy | sun4m | microSPARC | 50 MHz | 128 MB | Ноябрь 1992 / Авг 1993 | Июль 1994 | Июль 1999 |

| SPARCstation ZX | 4/30 | Sunergy | sun4m | microSPARC | 50 MHz | 96 MB | Авг 1993 | Март 1994 | |

| SPARCclassic X | 4/10 | Hamlet | sun4m | microSPARC | 50 MHz | 96 MB | Ноябрь 1992 | Май 1995 | Май 2000 |

Изначально SPARCclassic должна была называться SPARCstation LC, но была переименована вскоре после начала выпуска для того, чтобы избежать путаницу с SPARCstation ELC.

Читайте также: