Как называется электронная схема используемая в алу процессора

Вы здесь: Главная Процессор Процессор — аппаратный уровень. Арифметико логическое устройство (АЛУ)

Последовательное или параллельное?

Требуемую операцию можно выполнять для единицы данных (байт, слово, двойное слово, и т.д.) целиком, одновременно, параллельно, для всех ее разрядов (бит). Такие АЛУ называются параллельными . А можно выполнять операцию над каждым битом (группой бит) единицы информации по отдельности, друг за другом, последовательно. Такие АЛУ называются последовательными .

Но ведь последовательные АЛУ гораздо медленнее параллельных. Например, для байта, последовательное АЛУ потребует 8 циклов для выполнения операции вместо одного. Для чего вообще эти последовательные АЛУ нужны?

Например, последовательное АЛУ позволяет строить процессоры переменной разрядности, причем изменяемой "на лету", во время выполнения программы. И это может оказаться более важным, чем снижение быстродействия.

В реальном мире чистые последовательные и параллельные АЛУ (да и процессоры) не встречаются. Например, чуть ранее мы видели, как можно объединить два 4-х разрядных АЛУ. При этом обработка двух тетрад выполняется параллельно. Но ведь сигнал переноса не может быть обработан АЛУ старшей тетрады до тех пор, пока АЛУ младшей тетрады не закончит выполнение операции и не сформирует выходной сигнал переноса. Значит, для переносов обработка будет последовательной.

Первая версия

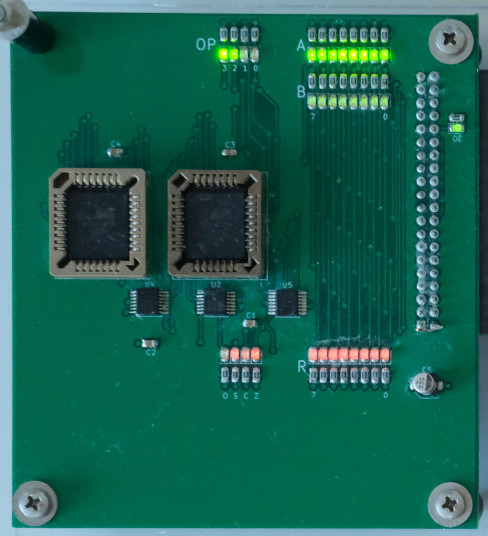

Когда я начал делать процессор, я хотел не тратить сильно много времени на АЛУ и скорее получить рабочий вариант, поэтому я сделал первую версию с помощью таблиц в ПЗУ. Простейший вариант мог бы быть таким:

Все входные сигналы подаются на вход ПЗУ, а с выхода снимаются выходные. Нужно всего лишь 2 22 = 4М слов по 12 бит. Такой микросхемы у меня не было, поэтому надо было что-то придумывать, и я придумал вот что:

Тут используется две микросхемы по 32к слов каждая. Левая отвечает за младшие 4 бита, а правая за старшие. Зеленая и красная линии передают информацию вверх или вниз. Передача вверх (зеленая линия) нужна, например, при сложении, чтобы передать перенос с бита 3 на бит 4, а вниз (красная), соответственно, при вычитании. Чтобы не возникало осцилляций (левая микросхема передала правой, правая левой и так по кругу), эти линии пущены через логическое И со старшим битом операции. Таким образом, операции, передающие информацию "вверх" (сложение, сдвиг влево), могут быть закодированы только кодами от 0 до 7, а передающие "вниз" (вычитание, сдвиг вправо) – от 8 до 15.

Первая версия АЛУ

Логические операции

Логические операции можно разделить на две условные группы: основную и расширенную. Список основных логических операций не велик:

- НЕ , отрицание, инверсия. Эта операция требует один операнд. Поэтому она может представлена как две операции: НЕ(а) и НЕ(b).

- ПОВТОР . Это просто передача выходного сигнала на выход, без каких либо изменений. Эта операция может показаться излишней, но это не так. В частности, занесение константы в регистр процессор выполняет именно с помощью этой операции АЛУ. Требует один операнд.

- И . В особых пояснениях не нуждается. Требует два операнда.

- ИЛИ . В особых пояснениях не нуждается. Требует два операнда.

- ИСКЛЮЧАЮЩЕЕ ИЛИ . Тоже не требует особых комментариев, на первый взгляд. Однако, эта операция не так проста. По сути, ИСКЛЮЧАЮЩЕЕ ИЛИ это не только логическая операция, но и арифметическая. Как арифметическая она формирует полусумму операндов. Почему полусумму? Потому что перенос не учитывается. Чуть позже мы это рассмотрим подробнее.

Расширенная группа логических операций может включать в себя И-НЕ, ИЛИ-НЕ, И(a, НЕ(b)), ИЛИ(a, НЕ(b)), и им подобные. Эти операции не обязательно реализуются специально, нередко они получаются как побочный эффект от схемотехнических решений при построении АЛУ.

При логических операциях перенос не используется.

Немного о разрядности

Здесь у нас два АЛУ, каждое из которых обрабатывает свою тетраду байта. При этом выходной сигнал переноса АЛУ младшей тетрады является выходным для АЛУ старшей тетрады. Без этого результат операции над байтом в целом был бы неверным.

То есть, переносы действительно являются не только внутренним делом АЛУ, даже в таком упрощенном случае. Разрядность сигнала переноса равна единице - это один бит. И он настолько важен, что для него предусмотрено место в слове состояния процессора. Но слово состояния процессора не тема сегодняшнего разговора.

Обратите внимание, что в некоторых процессорах в слове состояния есть дополнительный флаг межтетрадного переноса. Для нашего примера его легко реализовать с помощью сигнала Co АЛУ младшей тетрады.

В данном случае разрядность операндов/сигналов каждого АЛУ равна четырем. Я показал это на иллюстрации. Но, в общем случае, разрядность АЛУ может быть любой . В разумных пределах, конечно.

При этом даже одноразрядные АЛУ имеют практический смысл и практическое применение. На одноразрядном АЛУ можно построить последовательный процессор, который будет обрабатывать информацию бит за битом, последовательно.

Думаете, такие процессоры не имеют смысла и никогда не существовали? Ошибаетесь! Такие процессоры использовались, например, в настольных ЭВМ (программируемых калькуляторах) Wang. Я упоминал их в статье

Мы пока обошли стороной вопрос сигнала op . Это немного более сложный вопрос, так как операция может задаваться и кодом, и набором отдельных сигналов. Чуть далее мы рассмотрим это подробнее. Пока же будет достаточно точным говорить, что операция задается кодом. Соответственно, разрядность сигнала op определяется количеством различных операций, которые может выполнять АЛУ.

Обратите внимание, что разрядность кода операции никак не связана с разрядностью АЛУ !

Для данной статьи вопрос разрядности АЛУ не имеет большого значения. Ведь мы рассматриваем работу именно АЛУ, а не процессора, в котором оно используется.

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Сумматор

Осталось девять операций. Восемь из них могут быть выражены при помощи сложения или вычитания:

Что можно сделать на 12 транзисторах? Если схема аналоговая, это может быть, например, радиоприёмник или усилитель с достойными характеристиками. Для цифровой же схемы это катастрофически мало. Даже в такой простой микросхеме, как АЛУ К155ИП3 (74181), их значительно больше.

На самом деле транзисторов и здесь не 12, а 27, но из них в собственно АЛУ используются только 11 (двенадцатый транзистор, принудительно подающий логический нуль на вход переноса при выборе логических операций, не установлен). Остальные транзисторы задействованы в формирователе сигналов, подаваемых на входы АЛУ. При включении АЛУ в состав транзисторного процессора формирователь может и не понадобиться, если все необходимые сигналы там уже сформированы.

Как уложиться в это количество? Во-первых, сделать АЛУ однобитным, во-вторых, сократить количество операций до двух арифметических и пяти логических (у К155ИП3 и тех и других по 16, но и здесь их на самом деле больше), в третьих.

… выполнить АЛУ по необычной технологии DCTL (direct coupled transistor logic), позволяющей заметно сократить количество компонентов.

Симуляция выполнена в Falstad, этот симулятор удобен тем, что показывает направление протекания тока в виде «бегущих огней». Файлы: только полный сумматор и готовый АЛУ.

Для начала построим «АЛУ» с одной функцией — полный сумматор. Разобьём схему на две половины. Первая предназначена для подготовки входных сигналов для сумматора:

Выключателями можно задать два однобитных числа — A и B и сигнал переноса. Из них схема формирует четыре сигнала (четвёртый — тот же самый B, только инвертированный).

Вторая половина схемы — собственно сумматор:

Он представляет собой реализацию классического полного сумматора. На структурной схеме дополнительно показано распределение транзисторов по логическим элементам:

Чтобы всё это превратить в многофункциональное АЛУ, сначала переделаем формирователь входных сигналов таким образом, чтобы она формировала в прямом и инвертированном виде не только величину B, но и величину A:

Но поскольку автор планирует применить своё АЛУ в составе процессора на дискретных компонентах, такой формирователь, может и не потребоваться: там обе величины и так будут в прямом и инвертированном виде. Поэтому транзисторы формирователя и не входят в число транзисторов АЛУ. Да и без процессора можно просто взять переключатели с перекидными контактами. Ну а теперь — собственно АЛУ:

Четырьмя выключателями можно выбирать выполняемую АЛУ функцию. Ниже показаны только 7 основных:

Чтобы АЛУ не было «сферическим в вакууме», а могло получать сигналы извне, выключатели нужно заменить транзисторами. Поскольку транзистора, принудительно подающего логический нуль на вход переноса при выборе логических функций, пока нет, подавать нуль на этот вход в таких случаях нужно вручную.

Хотя на рисунке показаны всего 7 функций, можно попробовать все 16 сочетаний положений выключателей. Будут получаться, в частности, функции И-НЕ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, пропускание сигнала B насквозь, инвертирование того же сигнала.

Симуляция может преподносить сюрпризы. Знаете ли вы, что биполярный транзистор может работать при пропускании через него тока в обратном направлении? Так получается при некоторых сочетаниях входных сигналов. В аналоговом усилителе при этом уменьшается коэффициент усиления, но логические схемы продолжают работать так же, как в нормальном режиме.

Напряжение питания составляет +5 В. В симуляторе выбраны транзисторы общего применения структуры NPN.

Сумматор получается со сквозным переносом. Сигналу переноса приходится проходить через транзистора T8 и T9. Если это слишком медленно, нужно сначала проверить, как влияет на работу схемы цепь, подключённая к эмиттеру транзистора T8. Перенос можно также сделать быстрее, если выполнять его для двух бит одновременно.

Если нужен только полный сумматор, подойдёт и обычная диодно-транзисторная логика (DTL). Транзисторов понадобится всего два, а вот диодов… Можно заменить эти транзисторы лампами, получится то, что автор называет DVTL — diode-vacuum-tube-logic.

Верхняя часть схемы вырабатывает инвертированный сигнал переноса. Вторая вычисляет инвертированную сумму: СУММА = ( ( A или B или C вх ) и /C вых ). Данное выражение может быть представлено также как ( A и B и C вх ).

Структурная схема получается следующей:

Добавив ещё немного компонентов, можно принудительно подавать на вход переноса нуль или единицу. Тогда схема сможет выполнять операцию И (на входе переноса единица, на инвертированном выходе переноса — нуль), а также ИЛИ (на входе переноса нуль, на инвертированном выходе переноса — единица).

Чтобы подать сигнал «инвертированный C вых» на вход «C вх» схемы для следующего бита, нужен транзисторный инвертор. Либо можно принять правило, согласно которому между битами чередуется прямая и инверсная логика.

Всё это можно превратить в действующее АЛУ, рассчитав номиналы резисторов и добавив дополнительные компоненты для оптимизации «отзывчивости» схемы. Устройства, подключённые к входам, должны содержать ключи, замыкающие их на землю (для входов диодных «И»), либо соединяющие их с плюсом питания (для входов диодных «ИЛИ»).

Сдвиги

А вот эти операции нередко выполняются не АЛУ, а отдельными сдвигателями, которые могут включаться на входах АЛУ, но вне собственно АЛУ. Тем не менее, иногда АЛУ может выполнять и простые сдвиги на один разряд вправо или влево.

Статическое или динамическое (последовательностное)?

Во многих случаях выходные сигналы АЛУ напрямую определяются сигналами входными. То есть, АЛУ является комбинационным логическим элементом. Такое АЛУ и называется статическим.

Однако, последовательное АЛУ не может быть статическим. Обратите внимание, последовательное АЛУ не тождественно однобитному! Например, данные могут передаваться в АЛУ парами бит, всего 4 такта для байта. Такое АЛУ будет последовательным, но не однобитным. А выходной перенос, например, может формироваться лишь после обработки всей последовательности бит единицы информации.

Последовательное АЛУ для правильного формирования результата должно сохранять внутреннее состояние между тактами (шагами) выполнения операции. То есть, оно уже будет не комбинационным, а последовательностным логическим элементом. Такое АЛУ является динамическим.

Условные временные диаграммы работы статического (разрядность любая) и динамического АЛУ. Иллюстрация моя

Условные временные диаграммы работы статического (разрядность любая) и динамического АЛУ. Иллюстрация моя

Видно, что для статического АЛУ выходные сигналы появляются с некоторой задержкой относительно входных сигналов. А для динамического АЛУ все немного сложнее. Да, выходные сигналы по прежнему формируются с некоторой задержкой. Но операция теперь полностью выполняется за несколько тактов. Причем выходной перенос формируется уже после полного выполнения операции над всеми разрядами. Динамическому АЛУ нужен источник тактовых импульсов.

Еще раз обращаю ваше внимание, что речь идет именно об АЛУ, а не о процессорах.

В некоторых случаях на входах и выходе АЛУ, внутри АЛУ, имеются регистры-защелки для временного хранения обрабатываемой АЛУ информации. Например, это может потребоваться для процессоров с многофазной системой тактирования или процессоров с распараллеливанием выполнения команд.

Для выполнения операции в таких АЛУ требуется несколько шагов: запись данных в входные регистры, выдача кода операции, чтение выходного регистра. Такие АЛУ являются последовательностными, но не обязательно динамическими. Так как собственно операция может выполняться и параллельно.

Операции

Четыре бита кода операции дают 16 операций, куда влезает весь "джентельменский набор" арифметики и остается место еще для одной странной операции:

ADC , ADD – сложение (с переносом и без);

SBB , SUB – вычитание (с переносом и без);

INC , DEC – инкремент и декремент;

NEG – смена знака;

NOT – инверсия бит;

SHL , SHR , SAR – сдвиги на один бит;

AND , OR , XOR – побитовые логические операции;

EXP – сохраненный флаг переноса распространяется на все биты результата.

Интерфейсы

Заключение (промежуточное)

Сегодня мы "окинули взглядом" самые общие вопросы, касающиеся АЛУ и его работы. Процессоры могут включать в себя несколько разных АЛУ, с разной функциональностью, разным набором выполняемых операций.

В следующей статье займемся его внутренним устройством. При этом будем рассматривать лишь статические АЛУ. Надеюсь, будет интересно.

Every people has right on left

Chia ulo havas rajton sur levo

Каждый человек имеет право на лево

(Н. Фоменко)

CopyLeft (L) Юрий А. Денисов

(yudenisov)

Все права защищены

D.1.1. Элементная база АЛУ

На уровне логических схем АЛУ состоит из логических элементов, сумматоров, триггеров и некоторых других элементов.

Логический элемент – электронная схема, реализующая элементарную переключающую функцию. [А.П. Заморин и др. Вычислительные машины, системы, комплексы. Справочник. – М.: Энергоатомиздат, 1985. – 264 с.: ил. – стр. 31.] При реализации функций переключения входные переменные соответствуют входным сигналам, а выходной сигнал представляет собой значение функции. Всего существует десять логических элементов, реализующих десять логических (элементарных или сложных) функций. Их определения находятся в таблице D.1.I. Реализацию же логических элементов смотри в разделе C.1.2.

Реализуемые логические функции и обозначения логических элементов (Заморин, стр. 22.)

Логическая схема может реализовать сложную функцию алгебры логики, а может входить в состав другого функционального блока процессора (сумматора, дешифратора, регистра, триггера.)

Триггер – электронная схема с двумя устойчивыми состояниями, предназначенная для хранения одного бита информации. Триггер переходит из одного устойчивого состояния в другое при воздействии некоторого входного сигнала. Триггер имеет вход для установки в состояние 0 (X0) и в 1 (X1). На выходе выдается состояние триггера, которое выдается в прямом (Y) и в инверсном (Y1) виде. В компьютерах используют синхронизируемые и не синхронизируемые триггеры. Синхронизируемый триггер – это триггер, изменение состояния которого осуществляется только в момент подачи сигнала синхронизации V.

В зависимости от способа управления различают несколько типов триггеров: D- (с одним входом), RS- (с двумя входами), T- (со счетным входом), RST- (с двумя входами и счетным выходом) триггеры, и универсальные триггеры: JK- и DF-триггеры. Обозначение триггеров показано на рисунке D.1.1. [Заморин, рис. 1.1.стр. 21]

Триггеры, как правило, выполняются на логических элементах ИЛИ-НЕ, И-НЕ (рисунок D.1.2.) Если триггеры выполняются на логических элементах И-НЕ, то это триггеры с инверсным управлением; если на элементах ИЛИ-НЕ, то это триггеры с прямым управлением.

Рис. D.1.2. Схема реализации триггера - защелки на элементах И-НЕ (a) и ИЛИ-НЕ (b).

Триггер-защелка фиксирует состояние входного сигнала, поданного на один из его входов (рисунок D.1.2.)

Рис. D.1.3. Схема реализации RS-триггера на элементах И-НЕ.

RS-триггер – двухвходовый триггер с раздельными входами для установки в 0 или 1 (рисунок D.1.3.) При подачи единичного сигнала на вход R (-X0) триггер переходит в состояние 0 (Y=0, Y1=1), а при подачи на вход S (=X1) единичного сигнала – в состояние 1 (Y=1, Y1=0). Одновременная подача единичного сигнала на оба входа запрещена. Обычно RS-триггеры бывают синхронизируемыми (вход для синхронизации – V).

Рис. D.1.4. Схема реализации T-триггера.

T-триггер – одновходовый триггер со счетным входом: информация подается одновременно на два входа. При подаче сигнала состояние триггера меняется на противоположное (рисунок D.1.4.) Он, как правило, является не синхронизируемым, и позволяет не только хранить информацию, но и осуществлять сложение по модулю 2.

Рис. D.1.5. Схема реализации D-триггера.

D-триггер выполняет функцию задержки входного сигнала на один такт синхронизации (рисунок D.1.5.). Сигнал, появившийся на входе D (=X0) в момент времени T, задерживается в нем и появляется на выходе Y в момент времени T+1.

Триггеры с неустойчивыми состояниями называются вибраторами. Схема с одним неустойчивым состоянием (триггер Шмидта, одновибратор ) генерирует импульсный сигнал определенной длительности. Схема с двумя неустойчивыми состояниями называется мультивибратором и служит для генерации последовательности прямоугольных сигналов. Он используется тактовым генератором.

Рис. D.1.6. Реализация регистра.

Регистр – схема для приема, хранения и передачи n-разрядного блока данных Они используются для промежуточного хранения, сдвига, преобразования и инверсии данных. Регистры выполняются на триггерах и логических элементах. Их число и тип определяются разрядностью слова и назначением регистра. Если регистр не требует предварительного сброса данных (то есть установки всех его ячеек в ноль), то новые данные заменяют в нем старые. Схема регистра показана на рисунке D.1.6.

Рис. D.1.7. Реализация одноразрядного сумматора с переносом знака.

Сумматор – схема, выполняющая операцию арифметического сложения двух чисел. Различают одно- и многоразрядный (на всю длину суммируемых слов) сумматоры, полный сумматор (с приведением переносов) и полусумматор (с запоминанием переносов).

В зависимости от числа входов сумматоры бывают двухвходовыми и трехвходовыми. В двухвходовом одноразрядном сумматоре на вход подаются два разряда суммируемых чисел, а на выходе формируется результат сложения разрядов по модулю 2 и перенос в следующий разряд. В трехвходовом одноразрядном сумматоре на вход подаются два разряда суммируемых чисел и результат переноса из суммирования предыдущих разрядов, а на выходе – результат суммирования по модулю 2 и перенос в следующий разряд. Схема трехвходового сумматора показана на рисунке D.1.7.

Дешифратор – логическая схема, преобразующая входное n-разрядное двоичное слово в единичный сигнал на одном из 2^n входов. Обратную функцию выполняет схема, называемая шифратором. Дешифраторы широко используются в устройствах управления для управления работой микропроцессорами.

Copyright © Юрий А. Денисов. 2000-2002 г.

В настоящее время проект закрыт (в версии 1.00.3 alpha). Автор приносит извинения за прекрашение разработки.

Всем привет! Продолжаю серию постов про мой компьютер на логических микросхемах. Единственный модуль процессора, оставшийся до сих пор без внимания, – это АЛУ , про него и пойдет сегодня речь.

Арифметические операции

Основные арифметические операции так же просты:

- Сложение .

- Вычитание .

- Увеличение . Инкремент, +1. По сути, это сложение. Но операция настолько востребована, что часто реализуется отдельно.

- Уменьшение . Декремент, -1.

- Смена знака . Смена знака числа не тождественна инверсии.

К расширенным арифметическим операциям относятся:

Да, мы все еще со школы знаем, что умножение и деление, вместе с сложением и вычитанием, являются основными действиями арифметики. Но их аппаратная реализация сложна, поэтому далеко не все процессоры их поддерживают. А если и поддерживают, то не всегда на аппаратном уровне, может быть и микропрограммная реализация.

Реализация умножения и деления в АЛУ встречается не часто. Зачастую это отдельные блоки умножителей/делителей.

В специализированных случаях могут быть реализованы и дополнительные операции, которые позволяют облегчить выполнение более сложных, комплексных, операций. Но это не обязательно на уровне АЛУ.

В арифметических операциях переносы имеют важное значение. Так сложение отличается от исключающего ИЛИ тем, что учитывает переносы между разрядами.

Дополнительным моментом, который надо учитывать, является существование знаковых и беззнаковых чисел. Это не всегда влияет на схемотехнику АЛУ, собственно выполнение операций. Но часто требует дополнительных схемотехнических решений для формирования служебных признаков (флагов результата, например).

Мини блог

Реализация простых операций

Самая простая операция – EXP . Нужно всего лишь подать Cin на все входы соответствующего выходного буфера.

Сдвиги ( SHR , SAR , SHL ) тоже простые: на входы буферов подаются линии операнда со смешением на один бит в ту или другую сторону.

Для логической инверсии NOT можно использовать микросхему 74ACT240, которая аналогична 74ACT244, но имеет инвертирующие выходы.

Побитовые логические операции могут быть выполнены на паре микросхем 74AC08 для AND и 74AC32 для OR (плюс буфер 74ACT244, конечно же).

Требования

АЛУ принимает на вход следующие сигналы:

A, B – операнды, каждый по 8 бит.

OP – код операции, 4 бита.

Cin – старый сохраненный флаг переноса, 1 бит.

Inv – флаг перемены операндов местами, 1 бит.

OE – активация выходного буфера.

R – результат, 8 бит.

Z – флаг нуля, 1 бит.

C – флаг переноса, 1 бит.

S – флаг знака, 1 бит.

O – флаг переполнения, 1 бит.

Никаких тактовых сигналов нет, то есть, АЛУ асинхронно: значения на выходе обновляются сразу, как только изменятся сигналы на входах.

Общие сведения об арифметико логическом устройстве

Арифметико логическое устройство - это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции:

- принимающая на два входа два операнда (например, содержимое двух регистров);

- формирующая на выходе результат операции.

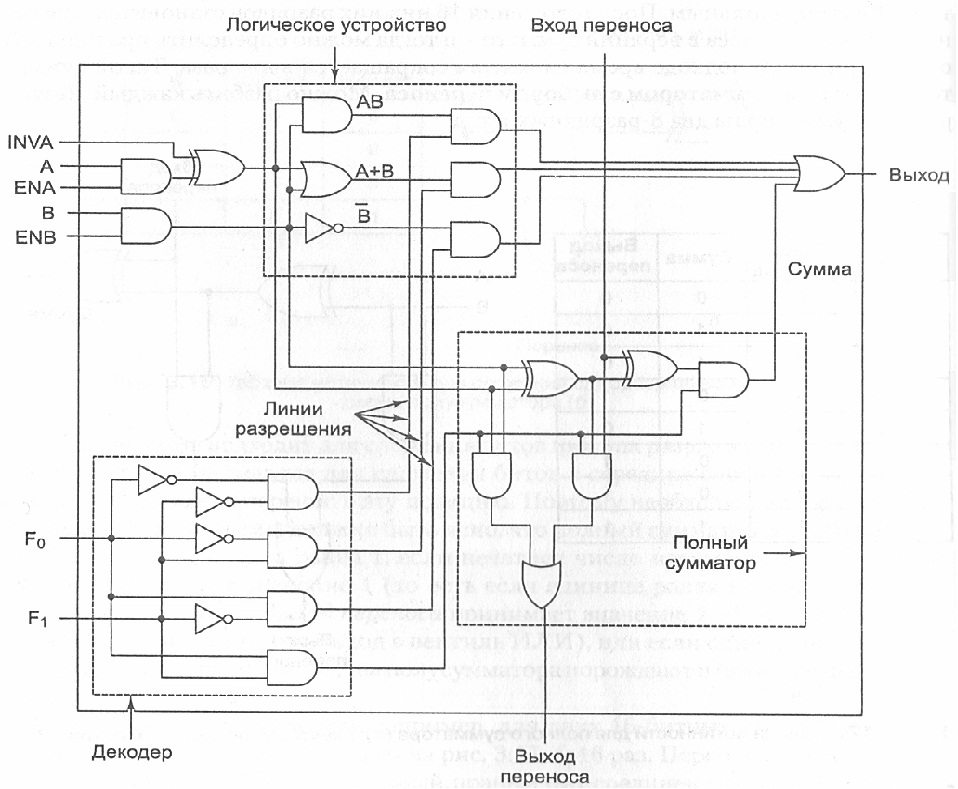

Большинство компьютеров содержат одну общую схему для выполнения операций И, ИЛИ и сложения над двумя машинными словами. Обычно такая схема для n-битных слов состоит из n идентичных схем для индивидуальных битовых позиций. На рисунке изображена схема одноразрядного АЛУ. Это устройство может вычислять одну из 4 следующих функций: А И В, А ИЛИ В, В- и А + В. Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1: 00, 01, 10 или 11 (в двоичной системе счисления). Отметим, что здесь А+В означает арифметическую сумму А и В, а не логическую операцию И. В левом нижнем углу схемы находится двухразрядный декодер, который порождает сигналы включения для четырех операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ. В верхнем левом углу схемы находится логическое устройство для вычисления А И В, А ИЛИ В и В-, но по крайней мере, один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И.

Схема одноразрядного АЛУ

Остальные три вентиля будут выдавать 0 независимо от значений А и В.АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить А-, установив INV А (инверсию А). При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INV А равен 0. В этом случае А и В просто поступают в логическое устройство без изменений. В нижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами. Одноразрядные схемы, подобные той, которая изображена выше, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. АЛУ можно представить как комбинационную схему, имеющую две входные шины (туда подаются два операнда) и одну выходную (на ней получается результат). Кроме того, АЛУ имеет несколько управляющих входов, сигналы на которых определяют выполняемую операцию(рисунок ниже).

Центральным элементом любой ЭВМ является процессор. А центральным элементом любого процессора является АЛУ - арифметико-логическое устройство. Именно АЛУ, в конечном итоге, выполняет все, даже самые сложные, операции. Но, как и многое настоящие труженики, зачастую остается в тени славы, которая достается процессорам и ЭВМ.

Даже при изучении архитектуры процессоров АЛУ лишь изображают символом на функциональной схеме, не углубляясь в детали его устройства. АЛУ слишком низкоуровневое, что там может быть интересного. Между тем, интересного там много.

Давайте сегодня попробуем заглянуть внутрь одного из базовых кирпичиков процессоров. Я не буду рассматривать какую либо конкретную ЭВМ, конкретный процессор, конкретную микросхему. Я расскажу немного об АЛУ в общем и целом. Но мы обязательно заглянем внутрь этого хитрого устройства.

Статья не является учебником. Это не копия каких либо книг или учебников. Это не компиляция других источников и статей. Как и другие статьи канала, это мой личный опыт.

Арифметико логическое устройство (АЛУ)

Архитектура ЭВМ

Что это вообще такое, АЛУ?

Разве собственно названия не достаточно для ответа на этот вопрос? Нет, недостаточно. АЛУ выполняет логические и арифметические операции, это правда. Но этого недостаточно для того, что бы перейти к более детальному рассмотрению его внутреннего устройства. Давайте начнем с самого простого

При все простоте и тривиальности, я не сомневаюсь, что вы все это и так прекрасно знаете, иллюстрация показывает важные моменты. Во первых, операция (в данном случае, сложение) выполняется над двумя операндами. В математике операнды назывались бы переменными. Операндов может быть и больше, но этот случай приводится к последовательности операций над двумя операндами. Операнд может быть всего один, но это частный случай, например

Суть от этого не меняется. Операция это то, что делается. Операнды это то, над чем выполняется операция.

АЛУ это не процессор! Это один из многих узлов процессора. АЛУ ничего не знает о переменных и их адресах. Не обращается к памяти для выборки данных. АЛУ работает с входными сигналами (a, b, op, Ci) которые и являются для него данными, формируя на их основе выходные сигналы (y, Co).

АЛУ на функциональных схемах обозначается таким вот забавным, похожим на шорты, символом. Это историческое обозначение. На функциональных схемах показывают не переменные, и даже не операнды, а сигналы. Поэтому наши два операнда превратились в два сигнала, a и b .

Выполняемая операция теперь тоже сигнал, op . Мы должны обязательно передать этот сигнал в АЛУ, именно он определяет, что АЛУ будет делать с входными сигналами. На выходе, в результате выполнения заданной операции, будет сформирован сигнал y , это результат операции.

Но всё ли это? Нет, не все. Этого достаточно для выполнения логических операций ( почти всех), но арифметические операции порождают еще и понятия переноса и заема . На первый взгляд, это внутреннее дело АЛУ. Но на самом деле, перенос/заем могут быть и входным сигналом, и выходным. Чуть далее мы это увидим.

А значит, более точно будет вот так

Операция, в общем случае, выполняется над тройкой операндов. Результат операции представляется парой значений. Иллюстрация моя

Операция, в общем случае, выполняется над тройкой операндов. Результат операции представляется парой значений. Иллюстрация моя

Здесь я показал современное изображение АЛУ. Перенос/заем обычно называется просто переносом и обозначается С (от carry - переносить). Не смотря на то, что для операции вычитания это будет заем. Ci это входной перенос (i - in), а Co выходной (o - out).

Вторая версия

Использовать ПЗУ – это читерство, поэтому надо было делать вторую версию полностью на логических микросхемах. Общая схема АЛУ такая:

Операнды A и B подаются на мультиплексор, который меняет их местами, если на входе Inv единица. В зависимости от кода операции один из блоков OP1-OPn активируется и подает значение на выходную шину, а остальные держат свои выходы в состоянии высокого сопротивления. В качестве выходного буфера каждого блока используется микросхема 74ACT244.

Типы операций, набор операций

Поскольку устройство арифметико-логическое, разумно предположить, что оно выполняет логические и арифметические операции. При этом выполняемые операции зачастую просты, даже элементарны. А более сложные операции, которые можно разбить на несколько элементарных, выполняются уже процессором, на более высоком уровне. Это не обязательно так, но это самый распространенный случай.

Так же надо отметить, что информационные входы АЛУ (a и b) не обязательно равнозначны. Да и включение АЛУ в схему процессора в большинстве случаев не симметрично. Но это тема отдельного разговора.

Компоненты ПК

Архитектура ЭВМ

Читайте также: