Vga dac что это

Продолжаем обзор девелоперских плат на основе SoC с ядром ARM. На этот раз мы рассмотрим платы на SoC Cyclone V. Это не единственный SoC компании Intel, есть ещё Arria V, Arria 10 и Stratix 10, но цена плат на их основе вас точно не обрадует.

Также компания Terasic продаёт некоторые платы по сниженной цене при наличии студенческого билета («academic price»). Насколько это реально для российских студентов, я не знаю, но если кто-то имел опыт такой покупки, будет интересно узнать. Пишут, что, например, Digilent при запросе покупки по академической цене отсылает к российсим дистрибьюторам, у которых цены завышены в 2-3 раза. Может быть, Terasic поступает иначе.

Кроме продукции компании Terasic мы рассмотрим также две платы производства компании EBV. Другие компании, выпускающие продукцию на Cyclone V, делают в основном модули SoM, а не девборды, и в обзор не попали.

Terasic

Итак, приступим к обзору самих плат. Я не буду приводить здесь весь каталог плат Terasic, ограничившись только несколькими платами, которые я выбрал по собственным субъективным критериям.

Большим удобством является то, что все платы от Terasic имеют USB JTAG.

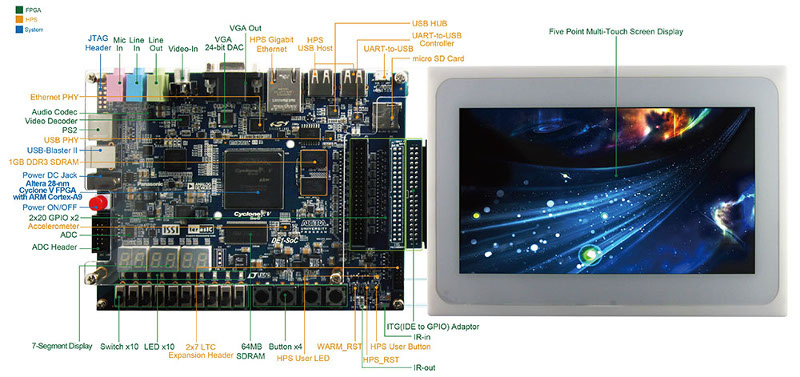

VEEK-MT2S

SoC: 5CSXFC6D6F31C6N

RAM: 1GB DDR3 SDRAM (HPS), 64MB SDRAM (FPGA)

Flash: нет

Ethernet: 10/100/1000 Ethernet

Размер: 158х228 мм

Цена: $660, академическая цена $559

Другие возможности:

- 24-bit VGA DAC

- 128x64 Dots LCD

- Audio 24-bit CODEC

- TV Decoder (NTSC/PAL/SECAM) and TV-In Connector

- ADC 500 KSPS x 12 бит х 8 каналов

- G-Sensor

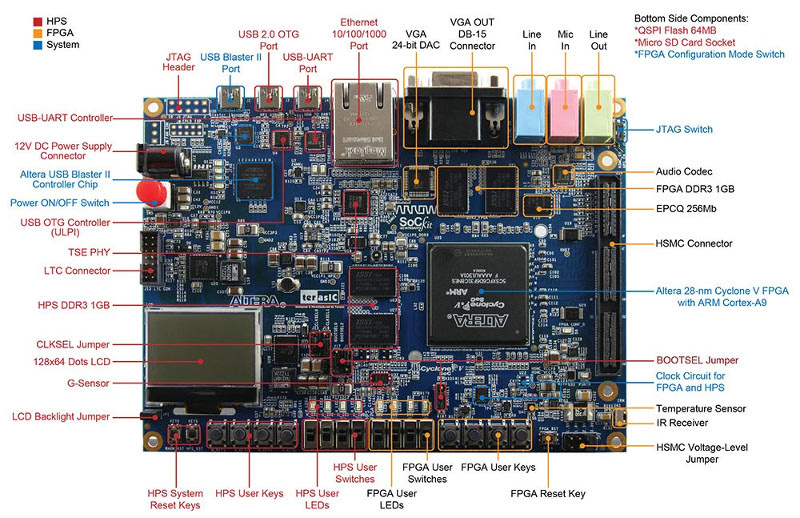

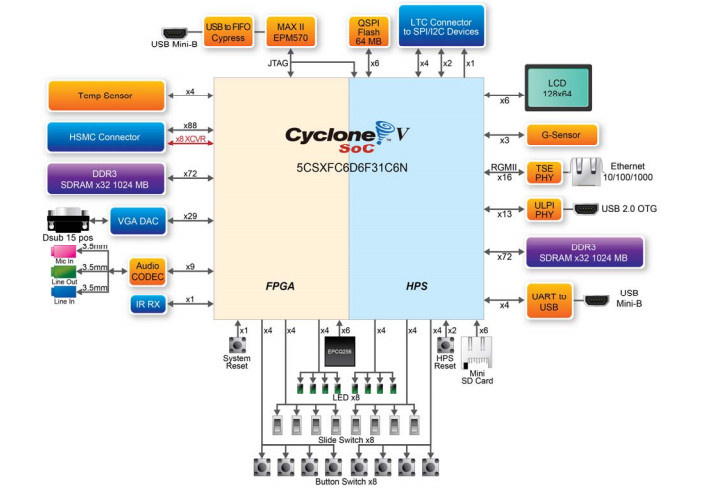

SoCKit

SoC: 5CSXFC6D6F31C6N

RAM: 1GB DDR3 SDRAM (HPS), 1GB DDR3 SDRAM (FPGA)

Ethernet: 10/100/1000

Flash: 128 Mb QSPI

Размер: 150 х 110 мм

Цена: $350

Другие возможности:

- IR emitter/receiver

- 24-bit VGA DAC

- Audio 24-bit CODEC

- TV decoder (NTSC/PAL/SECAM)

- ADC 500 KSPS x 12 bits x 8 каналов

- G-sensor (акселерометр)

- LCD 128 x 64

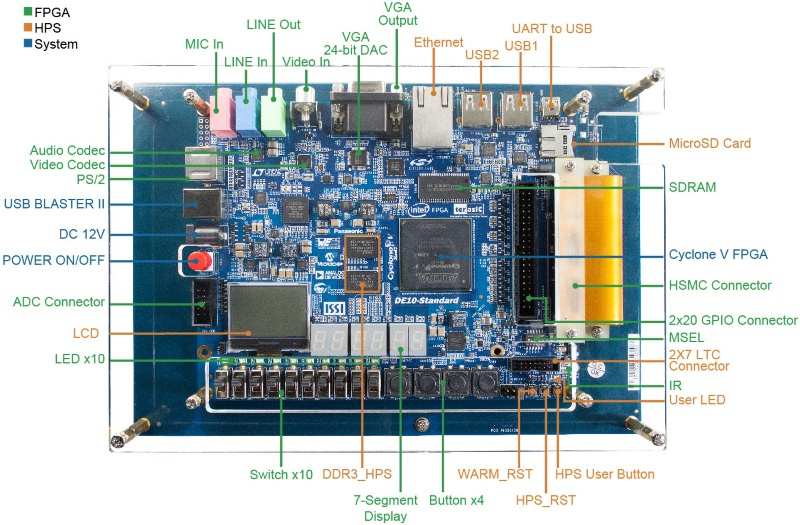

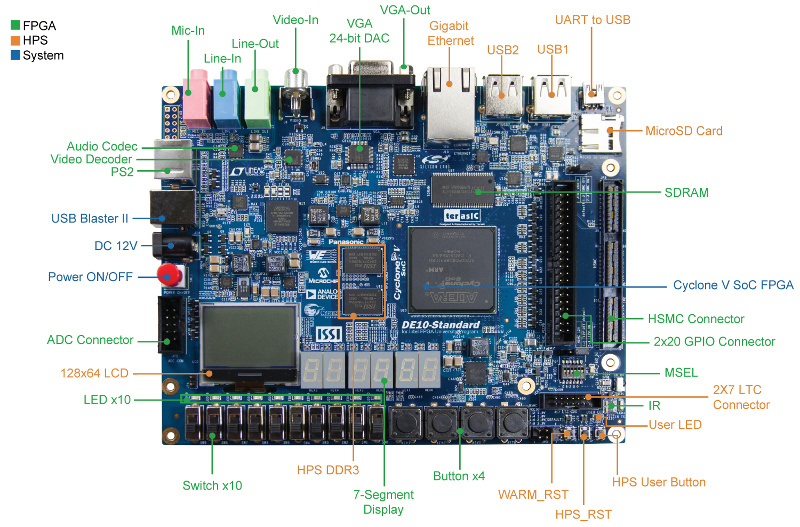

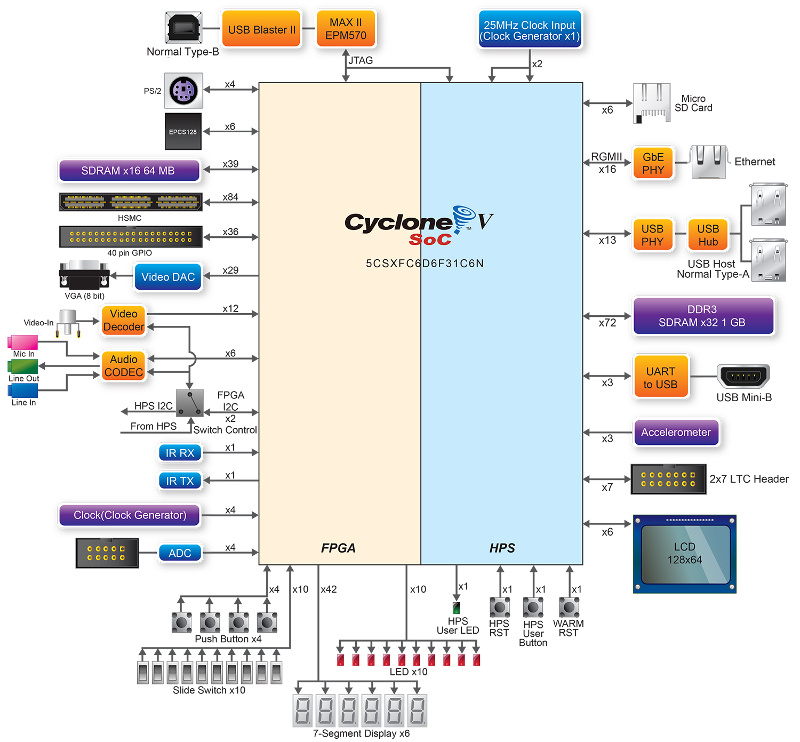

DE10-Standard

SoC: 5CSXFC6D6F31C6N

RAM: 1GB DDR3 SDRAM (HPS), 64MB SDRAM (FPGA)

Flash: нет

Ethernet: 10/100/1000

Размер: 166x130 мм

Цена: $350 (академическая цена $259)

Другие возможности:

- 24-bit VGA DAC

- 128x64 Dots LCD

- Audio 24-bit CODEC

- TV Decoder (NTSC/PAL/SECAM) and TV-In Connector

- ADC 500 KSPS x 12 бит х 8 каналов

- G-Sensor

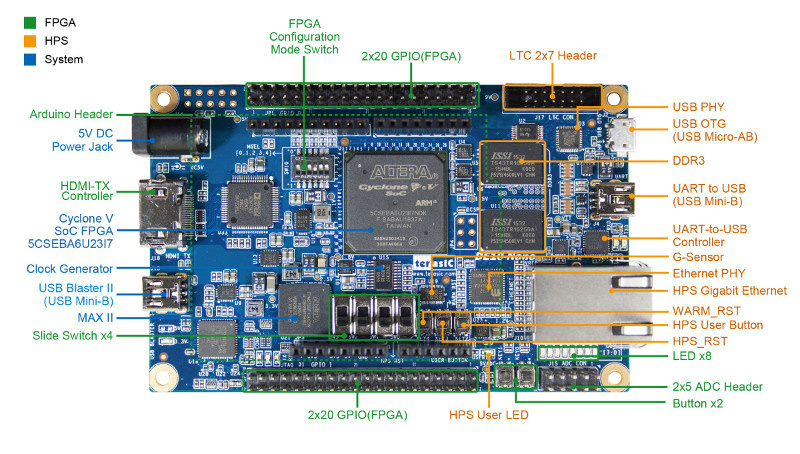

DE10-Nano Kit

SoC: SE 5CSEBA6U23I7

RAM: 1GB DDR3 SDRAM

Flash: нет

Ethernet: 10/100/1000

HDMI: есть

Arduino header: есть

Размер: 69х107 мм

Цена: $130 (академическая цена $99)

Другие возможности:

Программное обеспечение

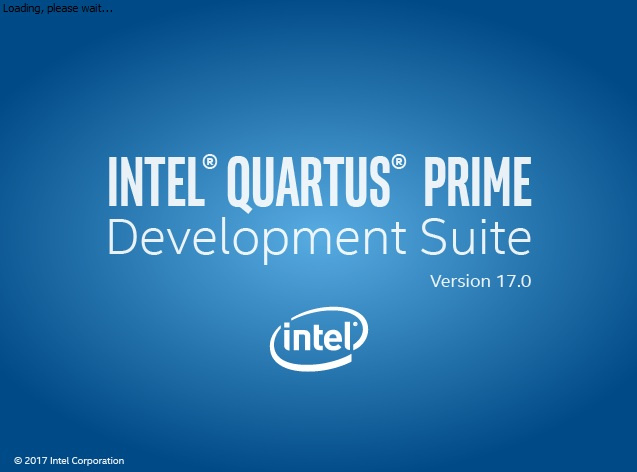

Как уже упоминалось в предыдущей части, для SoC компании Intel средой разработки проектов FPGA служит Quartus Prime, а средой разработки программного обеспечения — DS-5 Altera Edition. Она позволяет (в бесплатном варианте) разрабатывать приложения под Linux, разработка приложений Bare Metal, работающих без операционной системы, требует коммерческой версии DS-5. И Quartus Prime, и DS-5 существуют в версиях под Windows и под Linux.

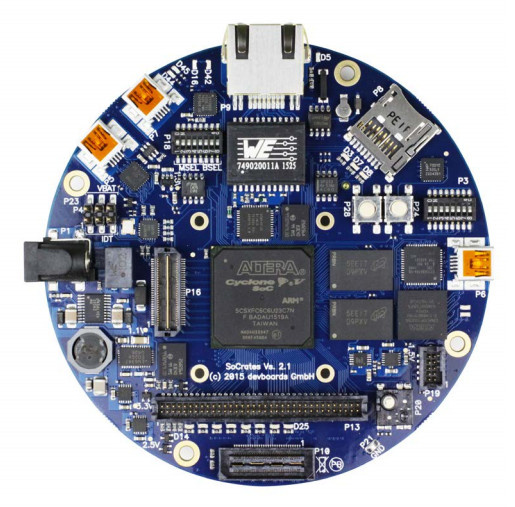

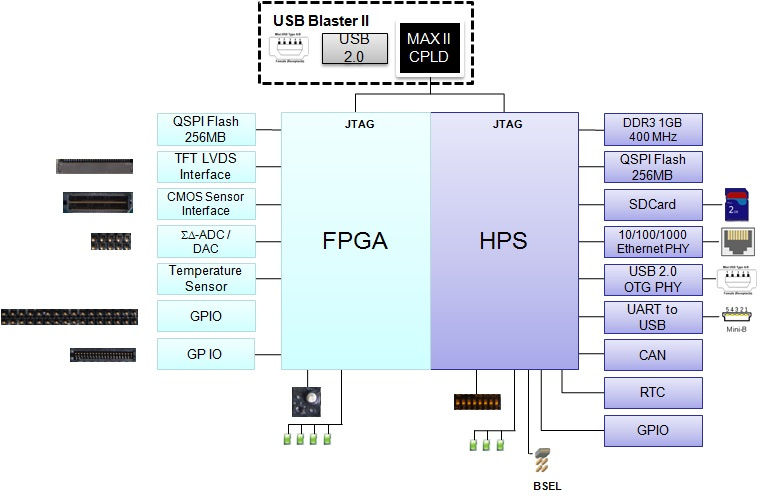

SoCrates II

SoC: 5CSXFC6C6U23C7N

RAM: 1 GB DDR3

Flash: 256 Mbit FPGA Configuration Device (QSPI) + 256 Mbit HPS Boot Device (QSPI)

Размер: 100 мм диаметр

Цена: 599 €

Вторая версия круглой платы от EBV. Больше ничего необычного в ней нет, и цена весьма немаленькая.

Qsys Connections

И теперь всё соединяем. Настройки для модуля Frame Reader «цепляем» к h2f master, интерфейс для передачи данных f2h slave. Соединяем Clocked Video Output с Frame Reader avalon_streaming_source -> din. Все тактируется outclk0.

И генерируем файлы, нажав Generate HDL . .

Как выше сказано, на плате 16 бит, а из модуля выходит 32 бита, поэтому нужно внимательно назначить пины в qsf-файле, либо отредактировать выход для себя удобным образом в top файле проекта. Нам нужны старшие биты каждого цвета, они более информативны, чем младшие.

Обратите внимание, что это первое и единственное место, где мы редактируем код. Больше это не потребуется.

Нам потребуется драйвер altvipfb.

Вернемся к параметрам Bits per pixel per color plane и Number of color planes in parallel в Frame Reader. В драйвере написано:

Число бит на один цвет только 8 и ширина слова должна быть больше или кратна 32. С чем же связано такое ограничение? Смотрим дальше и видим:

Становится ясно, что драйвер работает в режиме True color, записывая цвет в 32 битное слово ( более удобно выравнивать, чем 24 ), и работает он только в таком режиме.

Чтобы собрать этот драйвер, в конфиге ядра надо внести следующие изменения.

Для того что бы linux узнал, что у нас в FPGA есть фреймбуфер от Альтеры, в dtb надо прописать следующие магические слова:

В параметре range — диапазон валидных адресов, с которых драйвер будет читать, а в reg = — стартовый адрес и сколько адресов занято alt_vip. mem-word-width это параметр Master port width в Frame Reader.

Заходим на прибор и загружаем драйвера:

Затем проверяем, все ли хорошо с помощью dmesg, и смотрим, есть ли похожая строка:

Ура! Появился fb0:

Затем выводим консоль на экран, подключенный к плате:

Ставим icewm и запускаем с помощью startx:

Итого: мы получили графический контроллер, с минимальными знаниями HDL языков.

Как и материнская плата компьютера, видеокарта изготавливается на печатной плате, содержит процессор и оперативную память, есть система ввода-вывода (BIOS микросхема), которая хранит настройки карты и выполняет диагностику памяти при запуске. Процессор видеокарты, называемый графическим процессором (GPU), подобен центральному процессору компьютера. Однако GPU, специально разработан для того, чтобы выполнять сложные математические и геометрические вычисления, необходимые для графического рендеринга. У некоторых из самых быстрых GPU имеется больше транзисторов, чем у самого ЦП и следовательно большая производительность. Так же в процессе работы GPU выделяет большое количество тепла, поэтому его обычно снабжают теплоотводом или вентилятором.

|

| Типовое расположение компонентов видеокарты |

В дополнение к своей вычислительной мощности GPU использует специальное программное обеспечение, разработанное для того чтобы помочь ему проанализировать и использовать принятые данные более эффективно. Например, корпорации AMD и nVidia производящие основной объем имеющихся GPU на рынке, разработали свои собственные программные улучшения для повышения производительности GPU, так для улучшения качества изображения и использования процессора разработано:

Сглаживание (FSAA), которое приглаживает края 3D объектов, помогая им выглядеть более реалистично.

Анизотропная фильтрация (AF), заставляет изображения выглядеть более свежими.

Так же каждая компания разработала определенные методы и приемы, чтобы помочь GPU применить цвета, штриховку, текстуры и образцы, к примеру PhisX nVidia или Catalyst AMD.

Поскольку GPU создает изображения, он должен где-нибудь содержать уже завершенные, готовые картинки так сказать буфер хранения. Для этого в видеокарте используется оперативная память (RAM), она хранит данные о каждом пикселе, его цвете и расположении на экране. Часть RAM может также действовать как кадровый буфер, т.е., содержит в памяти завершенные изображения, пока не поступит команда от GPU вывести их на экран. Как правило, видеопамять работает в сверхвысоких скоростях, так как нужно в минимальный промежуток времени передать большой объем данных поэтому при изготовлении видеокарт производители стараются использовать память способную это обеспечить, на сегодняшний день DDR3 (DDR 4 будет поддерживать частоты от 2133 до 4266 МГц и в массовое производство выйдет предположительно в 2013 году).

Оперативная память непосредственно соединяется с цифро-аналоговым преобразователем, названным DAC (что-то подобное мы рассматривали в статьях про звуковые карты). Этот преобразователь, также названный RAMDAC, преобразовывает изображение в аналоговый сигнал, который может использовать монитор и отправляет изображение ему через кабель. У некоторых карт есть преобразователь, который может улучшить производительность и поддерживать больше чем один внешний монитор.

|

| У этой видеокарты Radeon X800XL есть DVI, VGA и соединения ViVo. |

Видеокарты соединяются с компьютером через системную плату. Системная плата подает питание к карте и позволяет ей связываться с центральным процессором компьютера. Более мощные видеокарты часто требуют большего количества питания, чем системная плата может им предоставить, таким образом, их снабжают разъемом дополнительного питания.

Соединения с системной платой обычно выполнено через один из трех интерфейсов, это:

- Взаимодействие периферийных компонентов (PCI) – в настоящие время не используется;

- Ускоренный графический порт (AGP) – в настоящие время не используется;

- PCI Express(PCIe).

PCI Express является самым новым из трех подключений и обеспечивает самые высокие скорости передачи данных и достаточный уровень питания видеокарты.

PCIe также поддерживает использование двух видеокарт на одном компьютере, работу порта PCIe рассмотрим в следующих статьях.

У большинства видеокарт есть два вывода для соединения с монитором. Это разъем DVI, который поддерживается ЖК мониторами и разъем VGA, для мониторов с ЭЛТ. Когда-то корпорация Apple выпустила мониторы, которые использовали собственный соединитель дисплея Apple (ADC). Хотя эти мониторы все еще находятся в использовании, компания Apple уже отказалась от выпуска мониторов с ADC и перешла к использованию соединения DVI.

В дополнение к соединениям карты, как с материнской платой, так и монитором, некоторые видеокарты снабжают и другими портами, вот некоторые из них:

- Для телевизора (S-video)

- Для аналоговых видеокамер: ViVo

- Для цифровых фотоаппаратов: (FireWire или USB)

- А некоторые видеокарты также содержат еще и телевизионные тюнеры для просмотра ТВ.

Использование видеокарт в современных компьютерах это так сказать не роскошь, а первая необходимость, а вот как не ошибиться при покупке видеокарты, как приобрести то что нужно и не жалеть о потраченных деньгах я постарался рассказать в статье «Основные 6 ошибок при покупке видеокарты или как выбрать видеокарту».

И в заключение данного материала хотелось бы сказать, что развитие компьютерных технологий способствует улучшению качества выдаваемой видеокартами картинки, и возможно, в скором времени качество графики в играх не будет уступать качеству художественных фильмов.

В своей предыдущей статье я рассказывал о подключении индикатора от телевизора к отладочной плате DE0-NANO. Однако получившаяся конструкция достаточна сложна и неудобна в работе — куча проводов, несколько источников питания, в том числе и 12В. Кроме того, из-за экзотичности индикатора, статья получилась не очень полезной. Поэтому далее в своих экспериментах я решил использовать обычный ЖК-монитор. О том, как подключить его к DE0-NANO — эта статья.

Внешний вид конструкции:

В Quartus система выглядит еще проще, чем в предыдущей статье — так как нет второго PLL:

Программирование Nios

Как я уже упоминал выше, для управление графической системой используется специальная библиотека, написанная в Altera.

Все функции, связанные с управлением SGDMA, находятся в файле «alt_video_display».

Наиболее важная — инициализация, вот пример ее использования:

Так как в данном примере вместо указателей стоят константы «ALT_VIDEO_DISPLAY_USE_HEAP», то библиотека разместит и видеобуферы, и дескрипторы в heap-памяти.

Так как число видеобуферов — 2, то будет использоваться двойная буферизация — в то время, пока на экран выводится один буфер, другой можно изменять.

После инициализации система готова к работе — данные из буферов автоматически выводятся на экран.

Формирование изображения должно осуществляться таким образом:

При написании программы столкнулся с очень плохим выводом изображения на монитор, которое решается постоянной отрисовкой вертикальной линии в нулевом столбце изображения. Эту линию приходится рисовать самой последней.

Видео работы программы:

Сначала отображаются кружки, как и в прошлый раз, а потом — синусоида.

Так как видеобуферов два, то каждый кружок приходится отрисовывать дважды — в каждом буфере.

Синусоида отрисовывается каждый раз заново, перед каждой отрисовкой буфер очищается. Расчет значений синусоиды — на ходу.

Программное обеспечение

Как уже упоминалось в предыдущей части, для SoC компании Intel средой разработки проектов FPGA служит Quartus Prime, а средой разработки программного обеспечения — DS-5 Altera Edition. Она позволяет (в бесплатном варианте) разрабатывать приложения под Linux, разработка приложений Bare Metal, работающих без операционной системы, требует коммерческой версии DS-5. И Quartus Prime, и DS-5 существуют в версиях под Windows и под Linux.

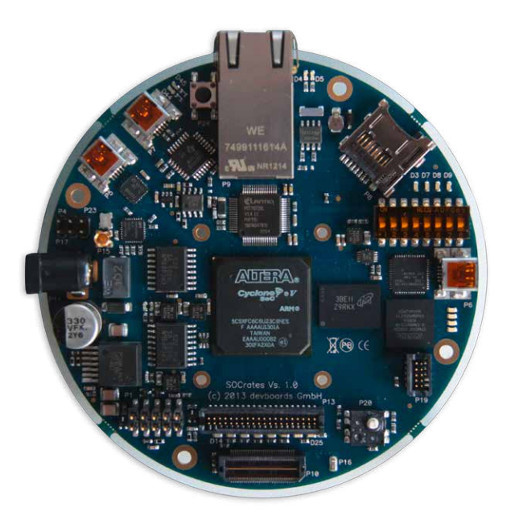

SoCrates

SoC: 5CSEBA6U23C7N

RAM: 128M DDR3

Flash: нет

Ethernet: 10/100/1000

Размер: 100 мм диаметр

Цена: 599 €

Плата необычной круглой формы, довольно старая и довольно дорогая. Более интересна её следующая версия, гораздо более оснащённая при той же цене (см. ниже).

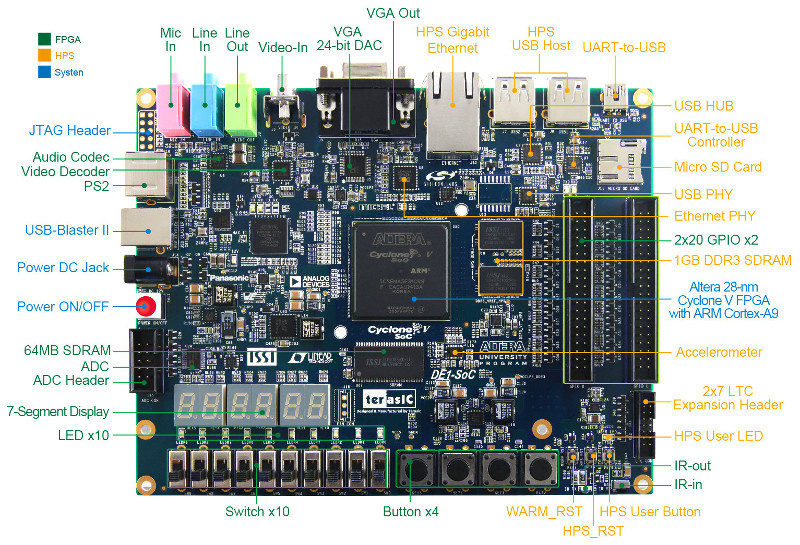

DE1-SoC Board

SoC: 5CSEMA5F31C6N

RAM: 1GB DDR3 SDRAM (HPS) + 64MB SDRAM (FPGA)

Flash: нет

HDMI: нет

Ethernet: 10/100/1000

Размер: 354 х 130 мм

Цена: $249 (академическая цена $175)

Другие возможности:

- 24-bit VGA DAC

- Audio 24-bit CODEC

- TV decoder (NTSC/PAL/SECAM)

- ADC 500 KSPS x 12 bits x 8 каналов

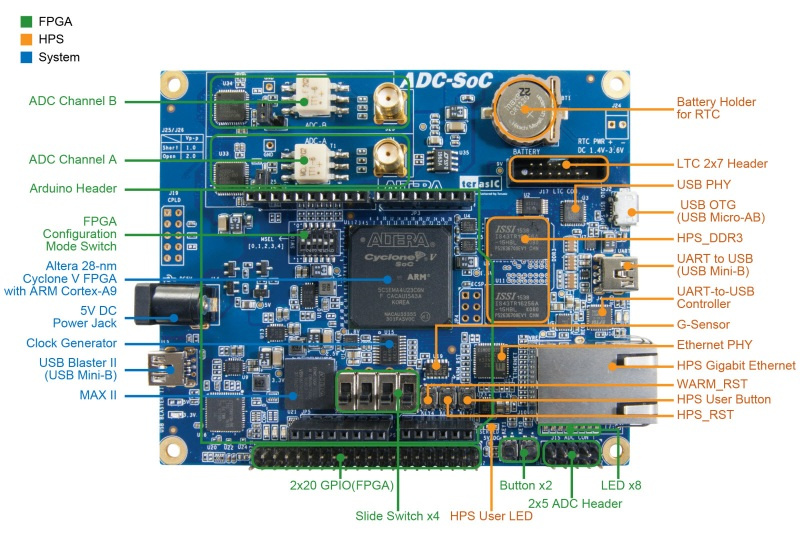

ADC-SoC

Производитель: Terasic

SoC: Cyclone V SE

RAM: 1 GB of DDR3 SDRAM

Flash: нет

Ethernet: 10/100/1000

JTAG: есть

Arduino header: есть

Размеры: 89x107 мм

Цена: $550

Другие возможности:

- 2 АЦП 14 bit, 150 MSPS

- G-sensor (акселерометр)

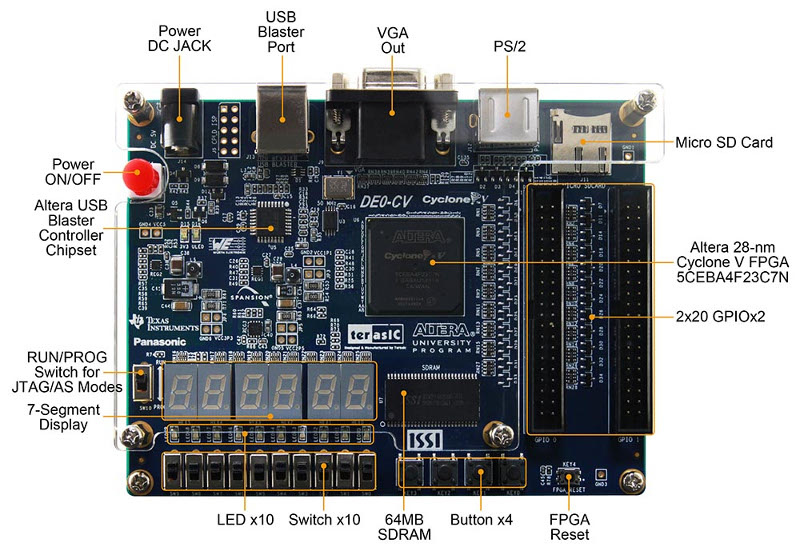

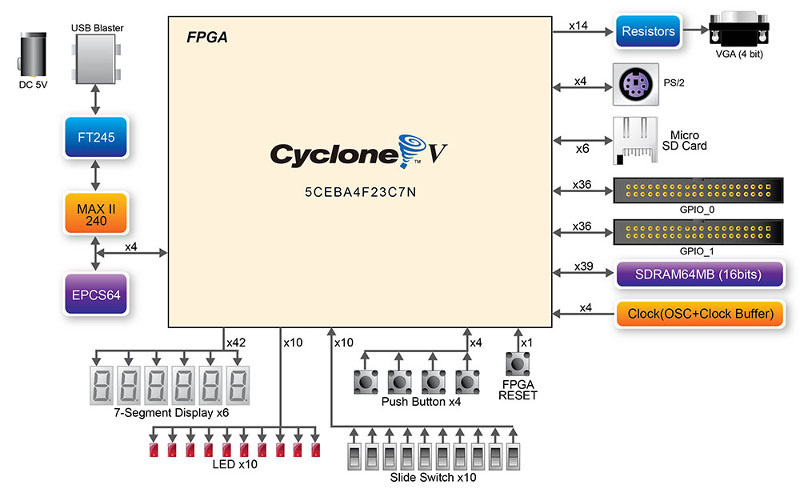

DE0-CV Board

SoC: 5CEBA4F23C7N

RAM: 64MB SDRAM

Flash: нет

HDMI: нет

Ethernet: нет

Цена: $150 (академическая цена $99)

Другие возможности:

Полезные ресурсы

Привет хабр — в этой статье я собираюсь поделиться своими успехами в освоении ПЛИС Altera Cyclone III. После мигания лампочками и игр со счетчиками — решил сделать что то более серьезное. Сделал я простейший VGA адаптер. Об основных его частях и пойдет речь. Статья больше ориентирована на начинающих, так как для опытных эта задача не составит труда, но для освоения, на мой взгляд — хорошая тренировочная задача. Эксперименты я свои провожу на отладочной плате Altera DE0. Описывать схему я буду на Verilog, Среда — Quartus II v 12.0. Итак — добро пожаловать под кат:

- Графический контроллер (Graphics Controller), посредством которого происходит обмен данными между центральным процессором и видеопамятью. Имеет возможность выполнять битовые операции над передаваемыми данными.

- Видеопамять (Display Memory), в которой размещаются данные, отображаемые на экране монитора. 256 кБ DRAM разделены на четыре цветовых слоя по 64 кБ.

- Последовательный преобразователь (Serializer или Sequencer) — преобразует данные из видеопамяти в поток битов, передаваемый контроллеру атрибутов.

- Контроллер атрибутов (Attribute Controller) — с помощью палитры преобразует входные данные в цветовые значения.

- Синхронизатор (Sequencer) — управляет временны́ми параметрами видеоадаптера и переключением цветовых слоёв.

- Контроллер ЭЛТ (CRT Controller) — генерирует сигналы синхронизации для ЭЛТ.

- Синхронизатор — частота 50 мегагерц для нас не очень удобна, поэтому её придется немного изменить

- Контроллер ЭЛТ, который будет выдавать сигналы синхронизации в соответствии с требованиями стандарта VGA

- Генератор картинки — будем использовать для отладки — блок будет рисовать простейшую картинку и выдавать её контроллеру ЭЛТ

Синхронизатор

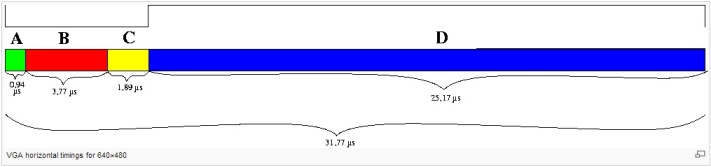

Начнем с того, что лезем на Английскую Вики и смотрим Signal timings для VGA, откуда узнаём, что частота синхрогенератора должна быть 25,175 МГц.

Вот нам и первая задача — сделать из 50 МГц — 25.175 МГц. Поможет нам в этом деле PLL или ФАПЧ.

При помощи Mega Wizard'а создаём наш PLL с нужными настройками. Для этого идем Tools/MegaWizard Plug-InManager. Там выбираем тип выходного файла Verilog HDL I/O ALTPLL и настраиваем его — устанавливаем входную частоту и затем её преобразовываем. Нам нужно получить частоту 25,175 МГц, при этом мы можем только умножать и делить на целое число, то есть нам нужно перевести число 0,5035 в дробь. Можно умножить на 5035 и поделить на 10000, но заметим, что можно сократить оба числа на 5. Получаем дробь 1007 / 2000. При этом визард сам приблизит требуемый множитель доступной ему дробью. Включаем полученный модуль в проект подключаем на его вход наш клок с платы, а для выхода создаём wire, который потом куда нибудь заведем, главная цель этого пункта достигнута — получить частоту 25,175 МГц.

Контроллер ЭЛТ

Генераторы синхроимпульсов

Двигаемся дальше. Теперь нам нужно создать модули, которые выдают синхросигналы, удовлетворяющие таймингам горизонтальной и вертикальной синхронизации, то есть вот этому для горизонтальной синхрониции:

То есть мы должны перед выдачей данных подержать линию синхронизации в высоком состоянии время А, потом прижать к земле на время B, потом перевести в высокое состояние, подождать время C и только потом идет поток данных — лучик начинает пробегать строчку за время D и мы за это время должны успеть установить все пиксели с частотой 25,175 мегагерц и так для каждой строки. Вертикальная синхронизация работает почти так же, только вместо пикселей мы передаём строчки и за один период синхроимпульса отрисовываем весь кадр.

Задача определилась — создать блок, который реализует описанную выше последовательность, принимая на вход частоту VGA_CLK, из входов еще добавим, пожалуй, сигнал сброса. Реализация такого блока не проста, а очень проста:

При периоде 1/VGA_CLK = 0,03972194637537239324726911618669 микросекунд нам нужно 24 такта на A, 95 на B, 48 на C, и 640 на D. То же самое и для вертикальной синхронизации, но тут удобнее тактироваться не по тактам частоты в 25.175 мегагерц, а по восходящим фронтам сигнала горизонтальной синхронизации, тогда все задержки можно считать в периодах отрисовки строчки. Кроме того у нас есть область «холостого хода» на экране, реально — по тактам экран чуть больше, а рисовать мы должны только в видимой области, поэтому желательно еще, чтобы модуль нам сообщал текущие координаты лучика, да и если мы собираемся назначать каждому пикселю какой то цвет — без знания текущей позиции луча не обойтись.

Модуль вывода

Собственно импульсы сгенерированы, координаты точки известны, осталось только вовремя включать нужный цвет, пока лучик пробегает строчку — для этого создадим модуль, которому на вход идут сигналы синхронизации, частота 25,175 МГц, 3 шины цвета и координаты, а выход — 4х битный R-2R ЦАП для каждого цвета, ну и далее — VGA разъем

Для проверки системы — сгенерируем какую нибудь картинку — этот блок описан не мной, взял его из экзамплов алтеровских, ну тут в общем то не с чем разбираться — нам от этого модуля нужна только картинка

Получилась вот такая вот структурная схема:

Ну и видео работы:

В общем — первый шаг с созданию своей видеокарты сделан — осталось приделать видеопамять и связать это всё с внешним контроллером — например STM32. В перспективе хочется сделать, чтобы контроллер генерировал видеопоток и посылал его видеоадаптеру, а тот выводил на экран. О практическом смысле этого всего говорить конечно не стоит — вещи уже устаревшие и довольно примитивные, всё делалось лишь с целью обучения и закрепления навыков, где то конечно тут набыдлокодил, так что если есть какие то вопросы, советы и замечания — пишите в комментариях

Всем привет!

В одной из предыдущих статей мой коллега Des333 реализовал фреймбуфер для LCD, работающего на графическом контроллере ILI9341. Однако, его написание потребовало существенного опыта в разработке RTL-кода.

К тому же, не у каждого под рукой есть embedded LCD-дисплей, зато наверняка есть монитор с VGA-входом.Что же делать, если опыта разработки под FPGA мало, но есть SoC, а сделать что-то интересное хочется?

В этой статье мы расскажем, как разработать графический контроллер, имея на руках плату с SoC (Altera Cyclone V), дисплей с VGA и минимальные знания языков HDL (в нашем случае — Verilog).

Для примера будем использовать наши платки, но всё описанное заработает и на других.

Кому интересно, прошу под кат.

- Сначала немного про архитектуру взаимодействия

- Кратко про подключение к VGA

- Как получить прошивку, используя только Quartus Qsys

- Как объяснить ядру, что есть графический контроллер. Расскажу, что нужно добавить в dtb и собрать драйвера

- Как получить терминал и иксы на дисплее

Для вывода изображения на дисплей нам нужны фреймбуффер, драйвер и модуль развёртки, который обеспечит связку между процессором и дисплеем, а также обеспечит непрерывное обновление кадров.

В SoC'е к ARM ( также называется HPS — Hard Processing System ) подключенна DDR3 память (1 GB в нашем случае), в ней и будет находится наш фреймбуффер. А в FPGA будет модуль, который нам нужно будет сделать с помощью Qsys.

- Драйвер настраивает модуль в FPGA: после этого модуль готов получать данные из SDRAM-контроллера и «разворачивать» их на дисплей

- В /dev/fb0 записываем картинку. Данные попадают во фреймбуфер в DDR

- Модуль в FPGA непрерывано читает фреймбуффер и обновляет экран

VGA ( Video Graphics Array ) — это видео интерфейс, использующий аналоговый сигнал для передачи цветовой информации. Формат сигналов и их поведение похожи на тевелизионный сигнал.

Список сигналов:

vga_vs_o — вертикальная синхронизация

vga_hs_o — горизонтальная синхронизация

vga_r_o — данные красной составляющей пикселя

vga_g_o — данные зеленой составляющей пикселя

vga_b_o — данные синий составляющей пикселя

Shield поддерживает 16 бит на цвет, а это значит, что на синий и красный выделяется по 5 бит, а на зеленый 6. ЦАП сделан по схеме R2R.

- Тактовая частота появления новых пикселей.

- Front porch — время гашения синхроимпульса.

- Back porch — время нарастания синхроимпульса.

- Sync — длительность синхронизации.

- Display Area — это момент времени, когда передаётся информация.

Времянки выглядят так:

- Front porch 40 pixels

- Back porch 88 pixels

- Sync 128 pixels

- Display Area 800 pixels

- Front porch 1 lines

- Back porch 23 lines

- Sync 4 lines

- Display Area 600 lines

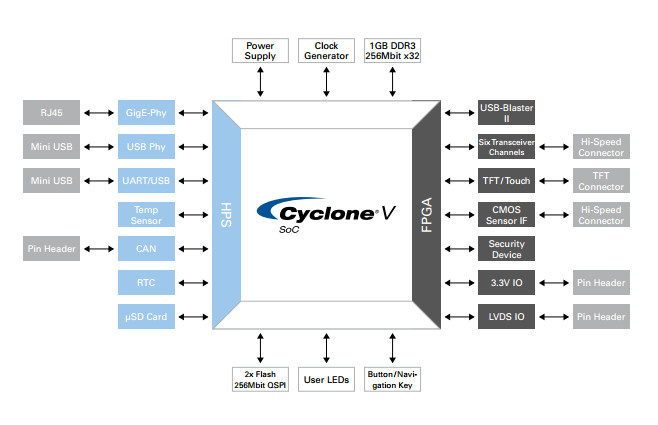

- HPS — это наш процессор.

- Frame Reader — это IP-ядро читает кадры, сохраненные во внешней памяти, и выводит их в виде видеопотока.

- Clocked Video Output — это IP-ядро, из Avalon-ST делает вывод в VGA подобном формате.

- Altera PLL — PLL для изменения тактовой частоты: нам нужно получить 40 МГц из 25 МГц, которые есть на плате.

Из процессора выходят AXI интерфейсы H2F и F2H, у IP-ядер Альтеры интерфейсы Avalon-ST и Avalon-MM , поэтому нужен еще модуль межсоединения ( Interconnect ), который должен конвертировать из одного интерфейса в другой и мультиплексировать потоки данных. Он появится автоматически при генерации файлов.

Подробнее про Frame Reader и Clocked Video Output можно посмотреть тут.

Как собрать прошивку и какие настройки нужны для HPS можно прочитать в этой статье.

Clocked Video Output

- Настройки синхронизаций ( vga_vs_o, vga_hs_o ), которые описывались выше

- Способ каким приходят данные ( он такой же как и у Frame Reader )

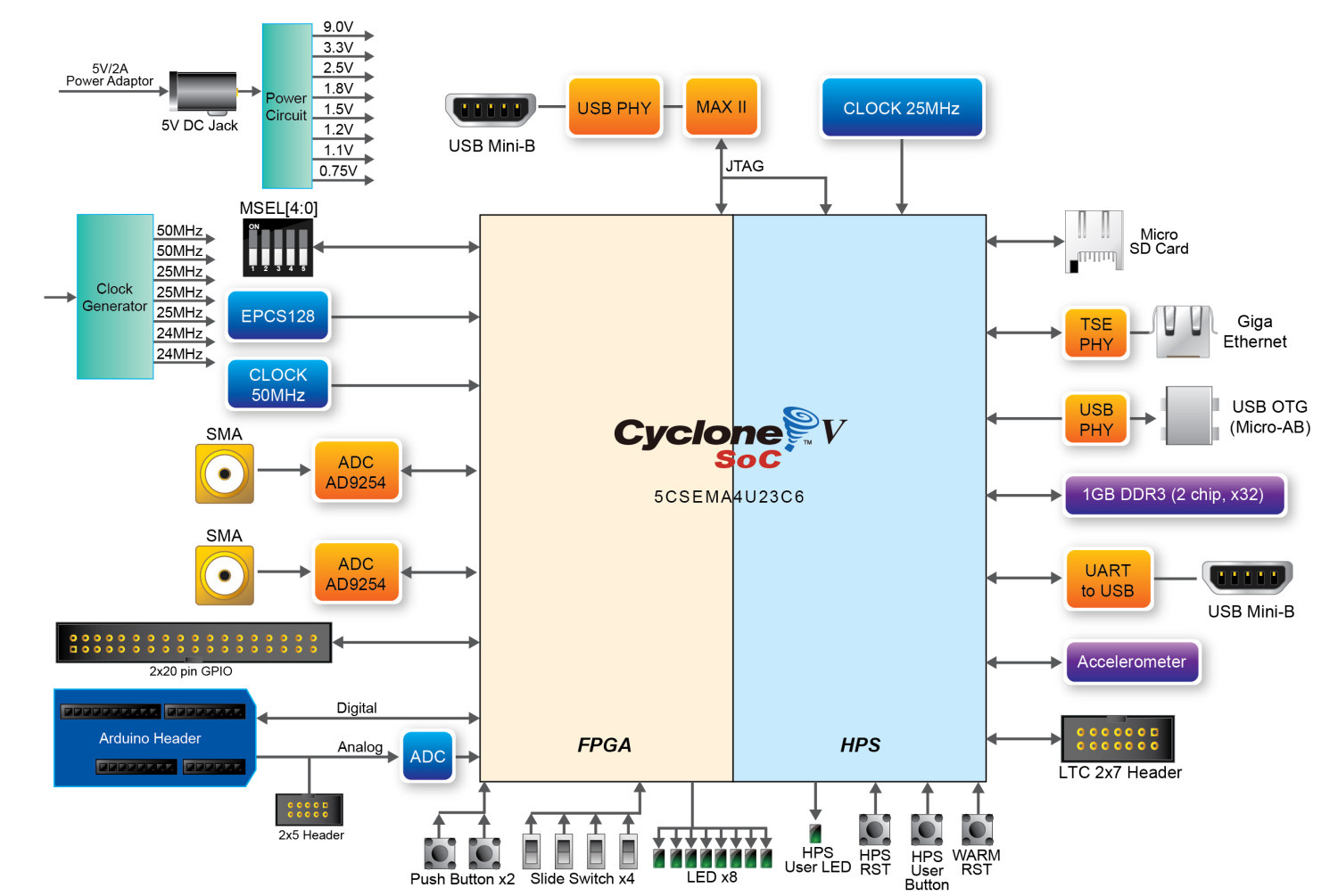

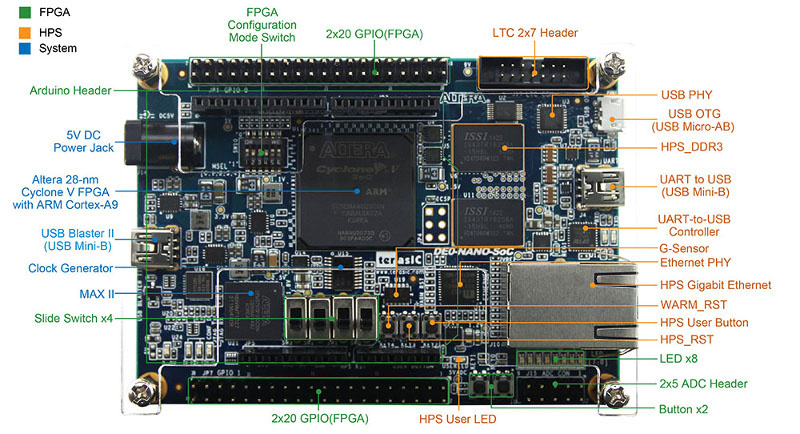

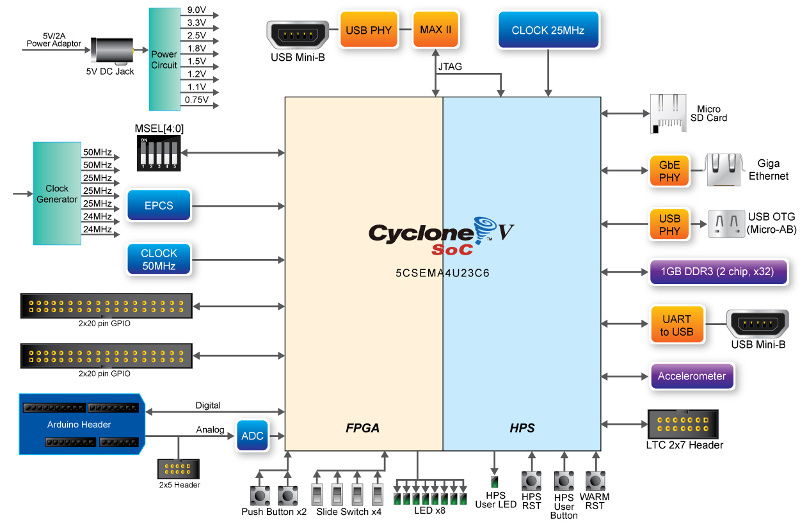

DE0-Nano-SoC Kit/Atlas-SoC Kit

SoC: SE 5CSEMA4U23C6N

RAM: 1GB DDR3 SDRAM

Flash: нет

Ethernet: 10/100/1000

HDMI: нет

Размер: 69x96 мм

Arduino hesder: есть

Цена: $99 (академическая цена $90)

Другие возможности:

Frame Reader

- Параметры FIFO на входе модуля

- Насройки передачи данных

- Количество активных пикселей

Altera PLL

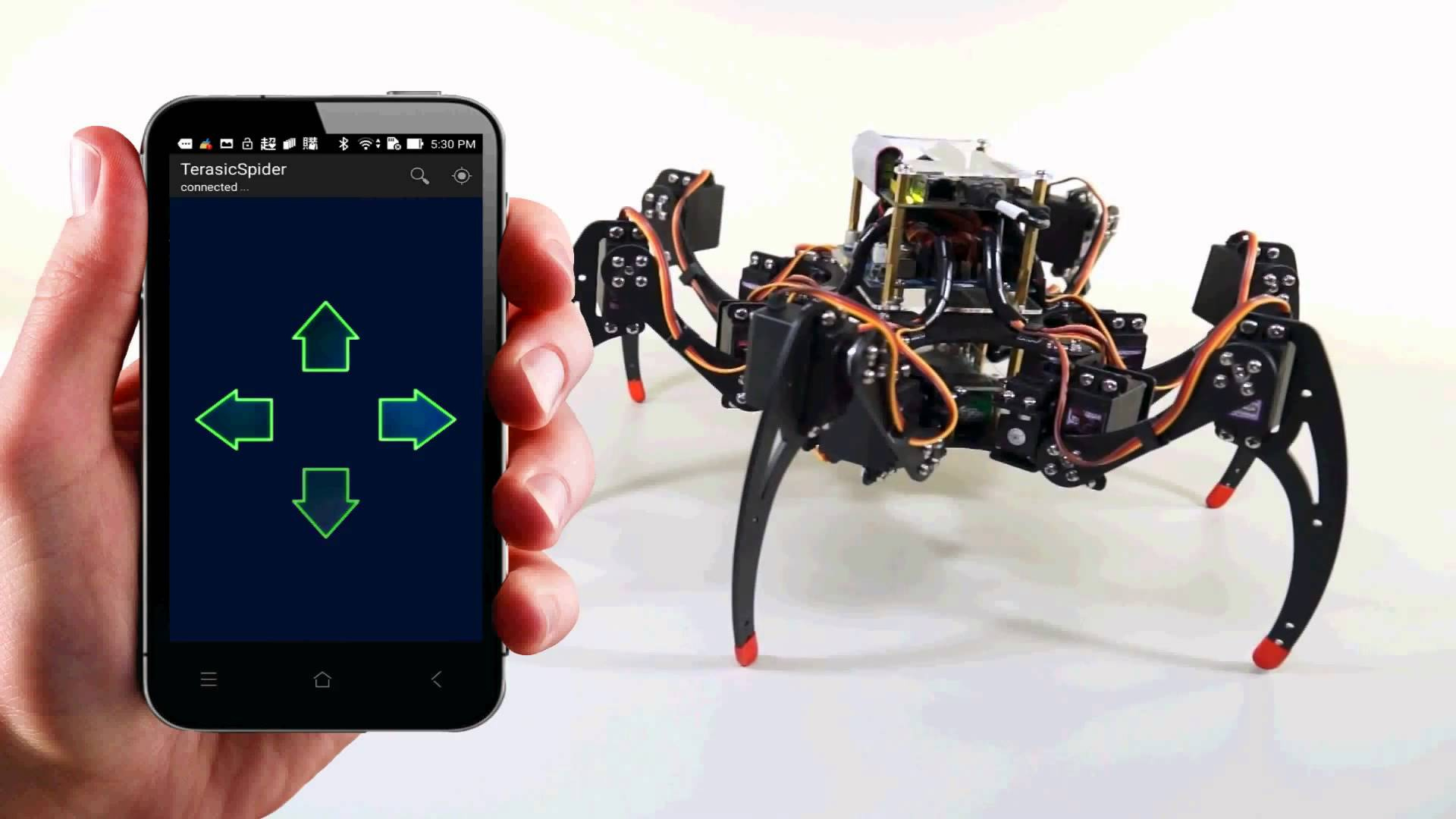

Terasic Spider

Мне кажется, дорого. Если есть желание заиметь такую игрушку, можно купить отдельно плату DE0-Nano ($99) и сделать шасси самому, потратив существенно меньшую сумму.

До сих пор мы рассматривали только платы от Terasic, но есть и другие производители плат на Cyclone V. Одним из таких производителей является компания EBV.

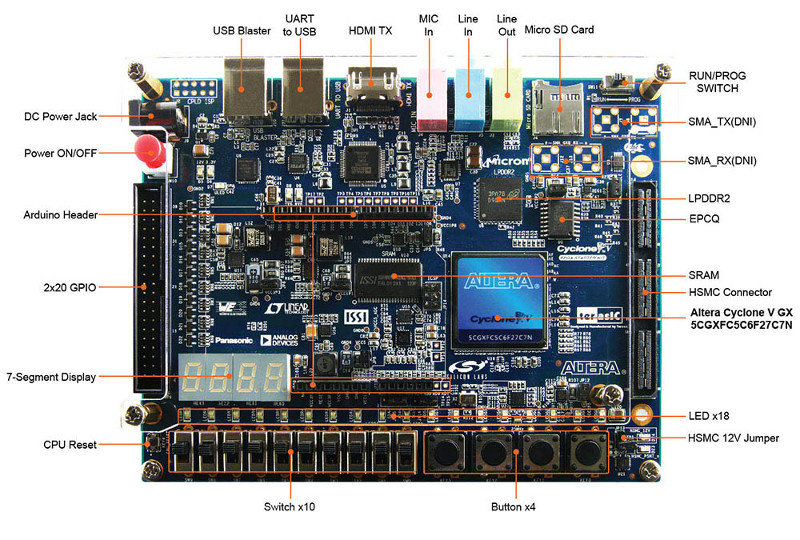

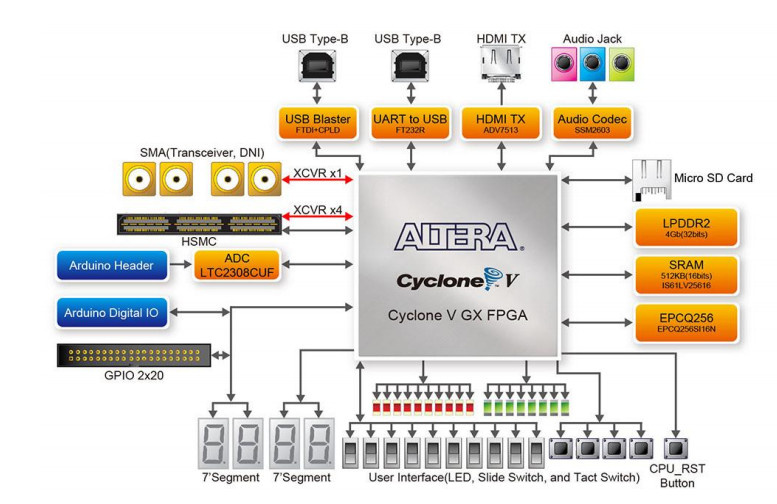

Cyclone V GX Starter Kit

SoC: GX 5CGXFC5C6F27C7N

RAM: 4Gb LPDDR2 (HPS), 4Mb SRAM SDRAM (FPGA)

Ethernet: нет

Flash: нет

HDMI: есть

Arduino header: есть

Размер: 150 х 116 мм

Цена: $179

Другие возможности:

- Audio 24-bit CODEC

- ADC 500 KSPS x 12 bits x 8 каналов

- G-sensor (акселерометр)

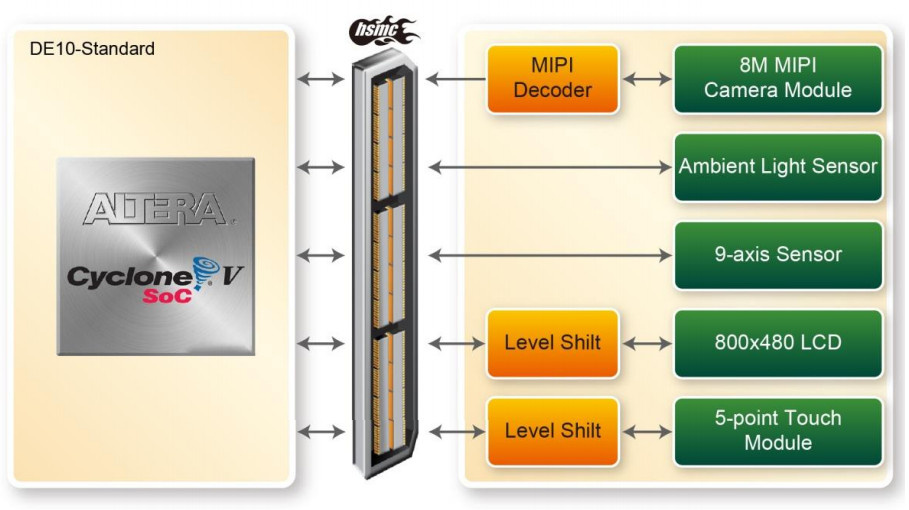

DE1-SoC-MTL2

Структурная схема сенсорного экрана. Структурную схему платы см. в описании DE1-SoC.

SoC: 5CSEMA5F31C6N

RAM: 1GB DDR3 SDRAM (HPS) + 64MB SDRAM (FPGA)

Flash: нет

HDMI: нет

Ethernet: 10/100/1000

Размер: 354 х 130 мм

Цена: $405 (академическая цена $330)

Другие возможности:

- 24-bit VGA DAC

- Audio 24-bit CODEC

- TV decoder (NTSC/PAL/SECAM)

- ADC 500 KSPS x 12 bits x 8 каналов

Читайте также: